Die IC-Gruppe des INT beschäftigt mit der Wandlung von Daten vom Analogen ins Digitale und umgekehrt. Teil des BMBF-Projekts 100GET (100 Gigabit Ethernet Transport Technologies) ist die Entwicklung von sehr schnellen A/D- und D/A-Umsetzern mit Wandlerraten von mehr als 25 GS/s bei Auflösungen bis 6 bit in CMOS-Technologie. Sie finden in der Übertragungstechnik vor allem bei den neuen Modulationsarten als Baustein im Empfänger bzw. Sender Verwendung.

Die Anforderungen an die Datenübertragungssysteme nehmen in den letzten Jahren durch die stark ansteigende Datenmenge stetig zu. Direkte amplitudenmodulierte Datenübertragung ist zwar momentan noch das meistgenutzte System, die Datenmengen lassen sich dabei aber in Zukunft durch die physikalischen Grenzen nicht mehr wesentlich steigern. Daher wird in Zukunft auf höhere Modulationsarten umgestellt werden. Ein Beispiel dazu ist Orthogonaler-Frequenzmultiplex (OFDM), wobei im Wesentlichen mehrere Signale auf orthogonal zueinander liegende Trägerfrequenzen aufmoduliert werden.

Analog/Digital-Umsetzer für 100 Gbit/s

Im Empfänger werden die Trägerfrequenzen dann wieder separiert woraufhin die durch den Kanal verzerrten analogen Daten-Signale einzeln an A/D-Wandler gegeben werden, die sie für die weitere digitale Verarbeitung wandeln. Durch mehrere orthogonale Signalströme pro Kanal lassen sich so mit einer entsprechenden Anzahl von A/D-Wandlern Datenraten von 100 Gbit/s und mehr erzielen.

25 GS/s 6 bit A/D-Umsetzer in 90 nm CMOS

Im Rahmen des BMBF-Projekts 100GET entwickelt das INT die kritischsten Komponenten (ADC und DAC) dieses Übertragungssystems in einer 90 nm CMOS Technologie. Die CMOS-Technologie ist für A/D-Umsetzer aufgrund der schlechten Eigenschaften wie beispielsweise geringer Verstärkung und niedriger Eingangsbandbreite eher ungeeignet, stellt aber die Möglichkeit der Integration mit großen digitalen Signalprozessoren (DSP) in Aussicht.

Die Umsetzer basieren auf dem Flash-Prinzip, welches Wandlungen in einem Zeitschritt ermöglicht. Am Eingang tastet ein Folge&Halte-Glied (engl.: Track and Hold circuit - T&H) das Signal ab und hält es konstant an den beiden parallel arbeitenden Zweigen (Master und Slave). Intern wird das Signal mit dem zweiten T&H wiederrum aufgeteilt und zwei parallel arbeitenden A/D-Umsetzern zugeführt. Eine eingangsseitige 3 bit Grobquantisierungsstufe mit darauffolgender dreistufiger Interpolation führt dann zu einer nominalen Auflösung von 6 bit des Wandlers. Diverse Kalibrationsmechanismen und interne digitale Schaltungen ermöglichen eine gute effektive Auflösung bei hohen Frequenzen und die Synchronisierung mit der Testumgebung.

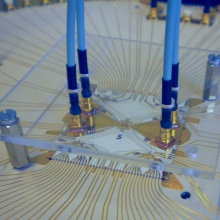

Das Layout und das Chipfoto der Schaltung ist in der folgenden Abbildung dargestellt. Der Umsetzer wird zur Messung mit vier ebenfalls in dem Projekt entwickelten DeMultiplexer-Chips (DeMUX) auf einer Dünnschichtplatine aufgebaut. Mithilfe eines sehr schnellen FPGAs lassen sich damit die empfangenen digitalen Ausgangssignale empfangen und weiterverarbeiten. Damit lässt sich der Umsetzer hinsichtlich der effektiven Auflösung ENOB (engl. für "Effective Number Of Bits") über dem Frequenzbereich charakterisieren. Detaillierte Informationen finden Sie in den Veröffentlichungen.

Digital/Analog-Umsetzer für 100 Gbit/s

Sender für optische Übertragungsstrecken, die auf modernen Modulationsverfahren (z.B. OFDM, N-QAM) basieren, benötigen sowohl sehr schnelle Digital-Analog-Wandler, als auch digitale Signalverarbeitungsblöcke (DSP). Ein Sender für optische Übertragungsstrecken mit 100 Gbit/s kann beispielsweise aus zwei DSP-Blöcken für die IFFT, vier Parallel/Seriell-Wandlern, vier 25 GS/s D/A-Umsetzern und elektro-optischen IQ-Modulatoren bestehen. Die DSP-Blöcke sind normalerweise in einer CMOS-Technologie realisiert, um die Chipfläche und den Leistungsverbrauch zu reduzieren. Wenn es gelingt, D/A-Umsetzer mit Abtastraten von bis zu 25 GS/s ebenfalls in CMOS-Technologie umzusetzen, kann der gesamte Sender auf einem einzelnen CMOS Chip integriert werden. Dadurch werden vor allem Kosten eingespart, da keine zusätzliche Aufbautechnik benötigt wird, um die D/A-Umsetzer mit den DSP-Blöcken zu verbinden.

28 GS/s 6 bit D/A-Umsetzer in 90 nm CMOS

Im Rahmen des BMBF Projekts 100GET wurden zwei Generationen von Digital-Analog-Umsetzern mit einer nominalen Auflösung von 6 bit für Abtastraten bis zu 28 GS/s in einer 90 nm CMOS Technologie entwickelt. Der Entwicklungsprozess beinhaltet dabei Schaltplanentwurf, Schaltplansimulationen, Layout des Schaltplans in 90 nm CMOS, Resimulationen des Layouts, Entwurf von HF-Platinen für den Aufbau der Wandler, Aufbautechnik, On-Wafer-Messungen für einfache Funktionstests und FPGA-Messtechnik für eine vollständige Charakterisierung der Umsetzer.

Die realisierten D/A-Umsetzer besitzen am digitalen Eingang Echtzeitschnittstellen mit einem Gesamtdatendurchsatz von bis zu 150 Gbit/s. D.h. man kann digital beliebige Signalformen berechnen und dann als reales analoges Ausgangssignal zur Verfügung stellen. Die Wandler eignen sich daher hervorragend für das Umsetzen komplexer Modulationen und können auch als "Arbitrary waveform generator" (AWG) eingesetzt werden.

Die D/A-Umsetzer basieren auf der Stromschalterlogik (CML). Mit der Stromschalterlogik lassen sich besonders schnelle Gatter entwerfen, da mit sehr geringen Logikpegeldifferenzen und differentieller Signalführung gearbeitet wird. Die Architektur der beiden Wandlergenerationen beruht auf dem Prinzip der Zeitverschachtelung. Ein 28 GS/s D/A-Umsetzer besteht aus zwei 14 GS/s Umsetzerkernen, die abwechselnd auf die positive und negative Taktflanke ihr analoges Ausgangssignal auf einen gemeinsamen Ausgang durchschalten, um das schnelle analoge 28 GS/s Signal zu erzeugen.

D/A-Umsetzer können eine binäre, unäre oder segmentierte Architektur aufweisen. Bei einer binären Architektur steuert jede Bitposition des Eingangswortes die entsprechende binär gewichtete Stromquelle an. Bei einer unären Architektur sind alle Stromquellen gleich groß dimensioniert. Die Stromquellen werden nicht direkt über das digitale Eingangswort angesteuert, sondern über ein Binär-zu-Thermometer (B2T) dekodiertes Wort. Eine segmentierte Architektur stellt eine Kombination und somit einen Kompromiss zwischen der binären und der unären Architektur dar. Die entwickelten D/A-Umsetzer verwenden eine segmentierte Architektur. Die zwei niederwertigsten Bitpositionen sind binär gewichtet, wohingegen die restlichen Bitpositionen unär gewichtet sind. Da aber zur Ansteuerung der unären Stromquellen kein B2T-Dekoder verwendet wird, sondern ein einfaches Verdrahtungsschema, spricht man von "Pseudo-Segmentierung".

Für die Wandlung des digitalen Signals in ein analoges Signal werden im hier entworfenen Umsetzer binär und unär gewichtete Stromquellen eingesetzt. In Abhängigkeit des am Umsetzer anliegenden digitalen 6 bit-Wortes werden Stromquellen auf einen Ausgang durchgeschaltet. Die Ströme werden anschließend über einen Lastwiderstand aufsummiert und in eine Spannung gewandelt. Die Umsetzerkerne bestehen aus binär und unär gewichteten Kaskodenstromquellen, Schaltern und Datentreibern, um die benötigten Pegel an den Schaltern zur Verfügung zu stellen. Weiterhin ist eine Auswerteeinheit auf dem Chip integriert, um die Synchronizität der digitalen Hochgeschwindigkeitseingänge der beiden Umsetzerkerne (bis zu 12,5 Gbit/s pro Kanal) mit einem FPGA zu überprüfen. Alle Schaltungsteile werden zeitrichtig über einem Taktbaum getaktet und versorgt. Da das Taktsignal mit bis zu 14 GHz auf dem Chip verteilt werden muss, wird das Taktsignal auf dem Taktpfad mit Spulen induktiv überhöht.

On-Wafer-Messungen der ersten und zweiten D/A-Umsetzergenerationen bestätigen Abtastraten von bis zu 28 GS/s und bitratenflexible Arbeitsweise. Die statischen Eigenschaften (INL, DNL, Mismatch) und der Leistungsverbrauch konnten mit der zweiten Umsetzergeneration noch einmal deutlich verbessert werden. Die Umsetzer der ersten und zweiten Generation sind ebenfalls auf Platinen und Dünnschichtsubstraten aufgebaut, um sie mit Hilfe eines FPGAs vollständig charakterisieren zu können.

Publikationen

2012

- T. Alpert, M. Werz, F. Lang, M. Masini, M. Grözing, and M. Berroth, “Arbitrary Waveform Generator Based on FPGA and High-Speed DAC with Real-Time Interface,” in Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Aachen, Germany, 2012, pp. 175–178.

2011

- T. Alpert, F. Lang, D. Ferenci, M. Grözing, and M. Berroth, “A 28GS/s 6b pseudo segmented current steering DAC in 90nm CMOS,” in IEEE/MTT International Microwave Symposium (MTT), Baltimore, MD, USA, 2011, pp. 1–4.

- T. Alpert, F. Lang, M. Grözing, and M. Berroth, “A 28 GS/s 6 bit CMOS DAC with Real-Time Interface,” in European Solid-State Circuits Conference Fringe (ESSCIRC Fringe), Helsinki, Finland, 2011.

- M. Grözing, F. Lang, T. Alpert, H. Huang, D. Ferenci, and M. Berroth, “25 GS/s 6 bit CMOS DACs and ADCs for 100Gbit/s Photonic networks,” in 12. ITG-Fachtagung Photonische Netze, Leipzig, 2011, pp. 37–44.

- F. Lang, T. Alpert, D. Ferenci, M. Grözing, and M. Berroth, “A 6 bit 25 GS/s flash interpolating ADC in 90 nm CMOS technology,” in Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Madonna di Compiglio, Trento, Italy, 2011, pp. 117–120.

2009

- T. Alpert, F. Lang, M. Grözing, and M. Berroth, “25 GS/s 6-bit Pseudo Segmented Current Steering DAC in 90 nm CMOS,” in European Solid-State Circuits Conference Fringe (ESSCIRC Fringe), Athens, Greece, 2009.

- J. Bozler, F. Lang, D. Ferenci, and M. Berroth, “Thermometer/Binär-Umsetzer für einen schnellen Flash Analog/Digital-Umsetzer in CMOS Technologie,” in Kleinheubacher Tagung, U.R.S.I. Landesausschuss in der Bundesrepublik Deutschland e.V, Miltenberg, Germany, 2009.

- F. Lang, T. Alpert, D. Ferenci, M. Grözing, and M. Berroth, “Design of a 25 GS/s 6-bit Flash-ADC in 90 nm CMOS technology,” in European Solid-State Circuits Conference Fringe (ESSCIRC Fringe), Athens, Greece, 2009.

Ansprechpartner

Markus Grözing

Dr.-Ing.Arbeitsgruppenleiter IC-Entwurf