Das INT bietet interessierten Studierenden die Möglichkeit, ihre Abschlussarbeiten in zukunftsorientierten Forschungsprojekten im Bereich der integrierten elektrischen und photonischen Schaltungsentwicklung zu absolvieren.

Allgemeine Themen/General topics

Main Task Categories

- Integrated circuit (IC) design

- Artificial neural network (ANN) modeling

Background

Artificial intelligence has found its way into more and more areas of life in recent years. This also applies to mobile applications with limited available energy. The energy efficiency of AI accelerators therefore plays a decisive role. Analog implementations are moving into focus, as they have considerable energy-saving potentials. By considering electrical voltages, currents and charges as continuous analog quantities to perform arithmetic operations, the energy required for inference can be significantly reduced compared to conventional digital calculation. At INT, we are working on an all-analog system, where the multiply-accumulate (MAC) operation and ReLU-activation operation is performed in analog.

Your Task

We are looking for very good students who want to help us to develop energy-efficient circuits or program hardware-aware models needed to train neural networks.

Exemplary Topics

- Modeling of analog circuit components in Python/Tensorflow/PyTorch.

- Design of highly energy- and area-efficient A/D and D/A converters

- Development of strategies to reduce or compensate mismatch at system level, circuit level or software level.

Your Profile

- Independent and goal-oriented way of working

- IC-design: Very good grade in the lecture Mixed Signal Integrated Circuit (INT), Verstärkertechnik (INT), Grundlagen Integrierter Schaltungen (INT) or in a similar lecture.

- ANN-modeling: Very good grade in lecture the Deep Learning (ISS) or in similar lecture.

We Offer

- Individual supervision and support

- Freedom to contribute and implement your own ideas

- State-of-the-Art process design kits for IC design

Contact

Art der Arbeit

- Schaltungsentwurf/Simulation

- Schaltungslayout

- HF-Systemsimulation

Hintergrund

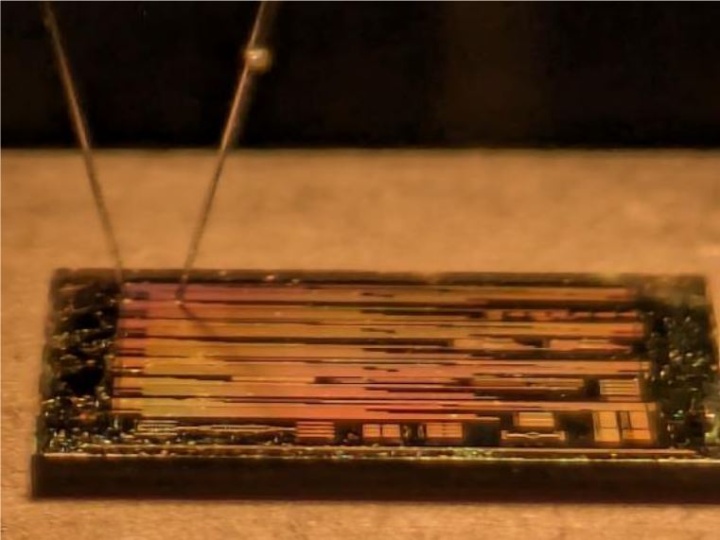

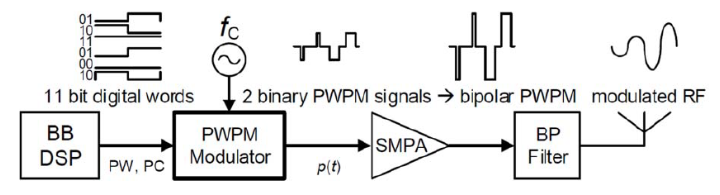

Um gleichzeitig die Effizienz und Linearität von hochfrequenten Leistungsverstärkern für Drahtlos- und Mobilgeräte zu verbessern, wird am INT der Ansatz eines volldigitalen Senderkonzepts verfolgt. Im Rahmen des von der DFG geförderten Forschungsprojekts „Hochfrequente Mehrstufen-Schaltverstärker im pulspositions- und pulsweitenmodulierten Betrieb zur effizienten Leistungsverstärkung von breitbandigen Mobilfunksignalen“ sollen dazu mehrstufige Schaltverstärker (ML-SMPA) in einer modernen FDSOI-CMOSTechnologie erforscht werden. Um den Dynamikbereich des Schaltverstärkers zu verbessern, wird die Amplitude des gefilterten HF-Signals zusätzlich zur Pulsweite in diskrete Ausgangsspannungs- (ML-VM-SMPA) oder Ausgangsstromstufen (ML-CM-SMPA) kodiert.

Aufgabenstellung

Abhängig vom Stand des Forschungsprojekts und der Art der Arbeit liegt der Schwerpunkt auf dem Entwurf eines mehrstufigen Schaltverstärkers mit Layout in Cadence IC, dem Entwurf von transformatorbasierten Netzwerken zur Leistungsaddition und Impedanzanpassung in ADS Momentum oder der Ansteuerung des Verstärkers. Gegebenenfalls sind Simulationen und Untersuchungen auf Systemebene in Matlab möglich.

Voraussetzungen

- Kenntnisse über CMOS-Schaltungen

- Grundkenntnisse über Hochfrequenztechnik

Ansprechpartner

Spezifische Themen/Specific topics

Themenüberblick

- FPGA-Entwurf mit VHDL

- Python-Programmierung

- Messtechnik

Hintergrund

Am INT werden integrierte Schaltungen (IC) zur Übertragung hochbitratiger Signale entworfen. Die Eingangsschnittstellen der ICs sind oft parallel ausgeführt, wobei jedeeinzelne Leitung von einer seriellen Hochgeschwindigkeitsschnittstelle eines FPGAs mit Daten versorgt wird. Da sie zusammen eine parallele Schnittstelle bilden sollen, müssen sie aufeinander synchronisiert werden. Die über die Schnittstellen zu sendenden Daten werden im FPGA in RAM-Blöcken zwischengespeichert. Die externe Kommunikation erfolgt über eine Ethernet-Schnittstelle mittels eines INT-proprietären Protokolls.

Deine Aufgabe

In diesem spannenden Projekt wirst du die Möglichkeit haben, eine flexible Hochgeschwindigkeitsdatenquelle zu entwickeln, die Teil einer Messumgebung für integrierte Schaltungen am INT ist. Zunächst erfolgt eine Einarbeitung in bereits bestehende Komponenten. Darauf aufbauend soll eine flexible Anpassung der Anzahl der Schnittstellen und des Speichers entwickelt werden. Die Datenrate soll in einem Bereich von etwa 1 bis 28 Gbaud einstellbar sein. Der Common-Mode der Ausgangssignale soll ebenfalls einstellbar sein. Die Konfiguration soll über eine GUI, die in Python entwickelt werden soll, erfolgen. Die Verifikation erfolgt an einem bestehenden Messaufbau.

Dein Profil

- Gute Vorkenntnisse in VHDL und Python

- Eigenständige und strukturierte Arbeitsweise

- Motivierte Herangehensweise an eine komplexe Aufgabe

- Empfohlen: Erfahrung mit AMD (Xilinx) Virtex-FPGAs und Vivado

Wir bieten

- Individuelle Betreuung und Unterstützung

- Raum, um eigene Ideen einzubringen

Kontakt

Hintergrund der Forschung

Die schnell wachsende Nachfrage nach Rechenkapazität für künstliche Intelligenz erfordert eine Reduzierung des Energiebedarfs von KI-Beschleunigern. Analoge Beschleuniger sind potentiell energieeffizienter als digitale und werden deshalb von Industrie und Wissenschaft erforscht. Am INT haben wir bereits ein rein analoges System entwickelt: zusätzlich zur Matrix-Vektor-Multiplikation ist die Aktivierungsfunktion durch eine analoge Schaltung implementiert. Dadurch wird die Ausgangsaktivierungen der Neuronen direkt weiterverwendet und an die nächste neuronale Schicht geleitet. Die Fläche und Energie für Cache-Speicher entfallen vollständig und die Latenzzeit wird minimiert.

Deine Aufgabe

Wir suchen motivierte Studenten und Studentinnen die mit uns energieeffiziente analoge Schaltungen zur Berechnung von künstlichen neuronalen Netzen entwickeln wollen. Diese Schaltungen sollen zukünftig noch schneller und effizienter rechnen und eine neue Generation des INT-KI-Chips ermöglichen. Die eingesetzte 22 nm FD-SOI CMOS Technologie bietet durch das Back-Gate-Biasing vielfältige Möglichkeiten und kreative Lösungen für den Schaltungsentwurf.

Diese Schaltungen kannst du entwerfen

- Entscheider-/Winner-Takes-All-Schaltung

- Analoges Schieberegister

- Schaltungen zur automatischen Korrektur von Prozessschwankungen (Mismatch)

- Digital-to-Time Converter (DTC)

Dein Profil

- Selbstständige und zielorientierte Arbeitsweise

- Sehr gute Leistungen in Vorlesungen zu integrierten, analogen Schaltungen oder CMOS/BJT-Transistoren, z.B. Mixed-Signal Integrated Circuits, Verstärkertechnik oder Grundlagen Integrierter Schaltungen

Wir bieten

- Individuelle Betreuung und Unterstützung

- Freiheit, eigene Ideen einzubringen und umzusetzen

- State-of-the-Art Prozessdesign-Kits und Entwurfswerkzeuge für den Schaltungs-Entwurf

- Vorbereitung auf eine Karriere oder Promotion im Bereich des analogen und mixed-signal Schaltungsentwurfs

Kontakt

Objective

- Simulation

- Optimization

Background

Photonic Integrated Circuits (PICs) have become a key component of modern communication technologies in recent years. They are used in a variety of commercial products, enabling complex optical functions such as pre-filtering and multiplexing. These PICs are typically fabricated on silicon platforms, similar to electronic circuits. To further increase the performance of these devices, the integration of advanced materials, such as subwavelength metamaterials, is essential. Metamaterials offer unique optical properties that are not found in naturally occurring materials, allowing for unique control over light propagation, refraction, and reflection. This enables the realization of highly compact and efficient photonic components, improving the functionality of PICs in applications like optical filtering, beam shaping, and enhanced light-matter interaction.

Your task

Your work will include electromagnetic simulations to analyze the properties of silicon-on-insulator (SIO) metamaterials and the use of optimization techniques to improve the device performance, with a particular focus on minimizing optical losses, reducing the device footprint, and improving the broadband behavior. The amount of work can be tailored to the type of thesis.

Your profil

- Experience in working with Python

- Knowledge in integrated photonics

- You have the ability to work independently and solve problems on your own

- Previous knowledge in electromagnetic simulation is beneficial

We offer

- Individual supervision and support

- Freedom to contribute and implement your own ideas

- Access to state-of-the-art facilities and advanced simulation tools

Contact

Objective

- Simulation

- Optimization

Background

Photonic Integrated Circuits (PICs) have become a key component of modern communication technologies in recent years. They are used in a variety of commercial products where they enable complex optical functions such as pre-filtering and multiplexing. These PICs are typically fabricated on silicon platforms, similar to electronic circuits. To further increase the versatility of these devices, the integration of specialized components such as polarization converters is essential. An integrated polarization converter allows the manipulation of the polarization states of light, which is critical for enhancing the functionality and efficiency of photonic systems, particularly in applications like optical signal processing and on-chip communication.

Your task

The project will focus on comparing and optimizing single trench TE/TM mode converters through simulations that analyze their passive characteristics. Additionally, the active behavior of these devices will be explored when integrated with a thermo-optical phase shifter for dynamic control. This will involve the development of a mode-selective metamaterial-based thermo-optical phase shifter.

Your profil

- Experience in working with Python

- Knowledge in integrated photonics

- You have the ability to work independently and solve problems on your own

- Previous knowledge in electromagnetic simulation is beneficial

We offer

- Individual supervision and support

- Freedom to contribute and implement your own ideas

- Access to state-of-the-art facilities and advanced simulation tools

Contact

Objective

- Software development

- Measurement technology (photonic)

Background

Photonic integrated circuits (PICs) have become a key component of modern communication technologies in recent years. They are used in various commercial products where they enable complex optical functions such as prefiltering and multiplexing. These PICs are typically manufactured on silicon platforms, similar to electronic circuits. To optimise their performance and expand their application areas, it is crucial to perform precise measurements and characterisations.

Your task

In this exciting project, you will have the opportunity to actively participate in the development of an automated measurement setup for PICs. Your main task will be to research and implement innovative optimisation algorithms to precisely control modern piezo-adjustable stages. By applying these algorithms, you will be able to autonomously identify the optimal coupling point, which in turn will maximise the efficiency and functionality of the photonic circuits. Your work will help drive the development of these groundbreaking technologies while providing you with valuable insights into the emerging field of photonic integration.

Your profil

- Initial experience in working with Python or Matlab

- Ability to perform precise manual work

- Enjoy optimising and searching for efficient solutions

We offer

- Individual supervision and support

- Freedom to contribute and implement your own ideas

- The opportunity to work on exciting photonic measurement setups and familiarise yourself with new technologies

Contact

Legende: BA: Bachelorarbeit, FA: Forschungsarbeit, MA: Masterarbeit

Neben den hier aufgelisteten Themen bieten wir auch kurzfristig Arbeiten zu unseren aktuellen Forschungsgebieten an. Teilweise können Masterarbeiten auch in abgespeckter Form als Bachelor- oder Forschungsarbeit durchgeführt werden. Die abgeschlossenen Arbeiten bieten Ihnen ebenfalls einen Überblick über das weite Themensprektrum des Instituts.Sprechen Sie bei Interesse einfach unsere Mitarbeiter an.

Die Projekte erfolgen in enger Zusammenarbeit mit renommierten nationalen und internationalen Forschungsinstitutionen und bieten Studierenden optimale Voraussetzungen, um ihre im Studium angeeigneten Fachkenntnisse an konkreten und praxisnahen Aufgabenstellungen einzusetzen und darüber hinaus anwendungsorientiert zu vertiefen. Spannende theoretische und praktische Aufgaben, die gemeinsam mit erfahrenen Doktoranden und Post-Docs erarbeitet werden, bieten hervorragende fachliche als auch persönliche Entfaltungsmöglichkeiten für den weiteren Berufsweg.

Abgeschlossene Arbeiten/Completed theses

2023

- T. Feller, “Effizienzsteigerung eines Schicht-7-Protokolls zum Datenaustausch über Ethernet auf einem FPGA.” 2023.

- T. Feller, “Entwurf eines Automotive Ethernet Messempfängers auf einem FPGA.” 2023.

- R. Kaps, “System Design, Model Building and Training of an Analog Neural Network based Equalizer for Optical Receivers.” 2023.

- L. Mockler, “Entwurf einer Abbildungsvorschrift zur Ansteuerung eines HF-Schaltverstärkers.” 2023.

- S. Wagner, “Entwurf und Aufbau einer Demonstrator-Leiterplatte für einen integrierten Arbiträrsignalgenerator.” 2023.

- J. Yao, “Design of an Energy Efficient Ring Amplifier for an Analog Multi-Bit Dynamic Memory.” 2023.

2022

- E. Dahm, “Entwurf und Aufbau eines klirrarmen Sinusgenerator mit Abtast-Halte-Glied zur Amplitudenstabilisierung.” 2022.

- R. Dietze, “Entwurf eines sukzessiven Approximationsregisters in einer 22nm CMOS Technologie.” 2022.

- C. J. Fuchs, “Elektro-Optischer Zweimoden-Modulator Basierend auf Plasmonischer Wellenführung.” 2022.

- F. Gleichauf, “Transimpedanzverstärker für einen Monolithisch Integrierten Optoelektronischen Empfänger.” 2022.

- J. Hinderer, “Entwurf eines Datenrückgewinnungsalgorithmus für einen Automotive Ethernet Messempfänger.” 2022.

- V. Leitz, “Charakterisierung optischer Verluste von Siliziumnitrid-Wellenleitern im sichtbaren Spektralbereich.” 2022.

- Y. Lu, “Integrated Circuit Design of Key Components of a SAR ADC in 22 nm FDSOI.” 2022.

- B. Lukat, “Transfer und Anpassung einer integrierten Multiplexer-Struktur mit Alterungs-Sensoren und Überarbeitung des Auswertekonzeptes.” 2022.

- R. Olivier, “Implementierung einer ethernet-basierten Kommunikationsschnittstelle für ein FPGA-Messsystem.” 2022.

- D. Sittard, “Integrierter Schaltungsentwurf eines Transkonduktanzverstärkers zur Verbindung analoger Neuronen.” 2022.

- V. Stadtlander, “Entwurf einer Transferschaltung für ein analoges dynamisches multi-bit Speicherkonzept.” 2022.

- S. Zhao, “Aufbau eines Sensorarrays zur Materialanalyse.” 2022.

2021

- P. Adam, “Entwicklung einer mehrkanaligen Ansteuerung für thermooptische Phasenschieber.” 2021.

- G. Choi, “Entwurf eines Ausgangsnetzwerks für einen breitbandigen linearen Verstärker.” 2021.

- A. Dogan, “Untersuchung und Optimierung von Elektroden in Silizium-organisch-hybriden Mach-Zehnder-Modulatoren.” 2021.

- J. Finkbeiner, “Integrierter Entwurf einer Optoelektronischen Eingangsschaltung für einen Empfänger in Glasfasernetzwerken.” 2021.

- C. J. Fuchs, “Elektro-Optischer Zweimoden-Modulator basierend auf plasmonischer Wellenführung.” 2021.

- A. M. Hemanth Kumar, “Circuit Design of Key Components for an Analog-to-Digital Converter in Optical Communications.” 2021.

- M. Leyzner, “Chip-integrierte photonische Systeme zur Polarisations-Modulation und Analyse von Licht.” 2021.

- S. Nau, “Design und Charakterisierung von hocheffizienten und breitbandigen optischen Glasfaser-Chip-Schnittstellen.” 2021.

- F. Probst, “Analyse und Weiterentwicklung eines Pulsgenerators für künstliche neuronale Netze.” 2021.

- T. Schillinger, “Implementierung eines digitalen Pulsgenerators mit mehreren synchronen Kanälen für Echtzeitanwendungen auf Basis von Einplatinen-Hardware.” 2021.

- L. Sun, “Implementierung und Weiterentwicklung eines laufzeiteffizienten Systemmodells in Python/Tensorflow für ein analoges Neuron.” 2021.

- X. Sun, “Zeitbasierte Eingangsstufe für ladungsbasierte Sensorsysteme.” 2021.

- J. Tonn, “Umsetzung eines Delta-Sigma-Algorithmus auf einem FPGA für die Mobilfunkkommunikation.” 2021.

- L. Wagner, “Entwurf eines Quadraturtakt-Systems.” 2021.

- S. Wagner, “Weiterentwicklung einer hardwarespezifischen Weiterentwicklung einer hardwarespezifischen KI-Bibliothek in Tensorflow für analoge künstliche neuronale Netze.” 2021.

- S. Wazynski, “Einstufiger analoger 4-zu-1 Multiplexer für 200 GBd-Signale in Bipolartechnik.” 2021.

- M. Widmaier, “Implementierung eines elektrooptischen Messplatzes zur Charakterisierung von Mach-Zehnder-Modulatoren“.” 2021.

2020

- V. Isik, “Optimierung eines ADC-Frontends für einen 400 Gbit/s - Empfänger.” 2020.

- A. Kabbaza, “Entwurf und Vergleich von Schaltungen für die Taktaufbereitung.” 2020.

- R. Klenk, “System-Studie zur chip-integrierten Anregung und Analyse von Fluoreszenz-Effekten in Mikrofluidik-Kanälen.” 2020.

- B. Lukat, “Effiziente Schaltung zur Übertragung von Ladung zwischen Kondensatoren.” 2020.

- L. Meyer, “Untersuchung und Design magnetisch gekoppelter integrierter Strukturen.” 2020.

- N. Miller, “Redesign einer FPGA-basierten Messumgebung mit hochbitratiger paralleler Schnittstelle.” 2020.

- V.-G. Mircea, “Minimierung des Rauschens von ESD Schutzschaltungen für Eingänge hoher Impedanz.” 2020.

- S. Salmani, “Untersuchung von rückseitenbasierten optischen Glasfaser-chip-Schnittstellen.” 2020.

- T. Schillinger, “Entwurf und Charakterisierung von Leiterplatten zum Aufbau eines Radar- ASICs in 22-nm-CMOS-Technologie.” 2020.

- M. Schubert, “Aufbau eines Laserversorgungsmoduls mit Stromquelle und Temperaturregelung.” 2020.

- C. Schweikert, “Optimierung integrierter optischer Bauelemente für die on-chip-Sensorik.” 2020.

- L. Sun, “Entwurf eines Systemmodells für ein analoges Mischsignalneuron.” 2020.

- P. T. Tran, “Rauschen und Nichtidealitäten in analogen neuronalen Netzwerken und ihr Einfluss auf die Korrektklassifikationsrate: Noise and non-idealities in analog neural networks and their influence on the correct classification rate.” 2020.

- P. Tritschler, “Charakterisierung von Raman- und Fluoreszenz-Effekten in Chip-integrierten Wellenleitern.” 2020.

- Y. Wang, “Optische Bauelemente für die spektrale Signalanalyse in der Silizium-auf-Isolator-Plattform.” 2020.

- F. Westhäußer, “Entwicklung eines Daten-Simuators für einen Destiny+ Staubanalysator.” 2020.

- F. Westhäußer, “Entwicklung eines yearn-Simuators für einen Destiny+ Staubanalysator.” 2020.

- M. Wittlinger, “HF-Schaltverstärker in FDSOI CMOS-Technologie.” 2020.

- Y. Zhang, “Untersuchung und Entwurf von Schutzkonzepten gegen elektrostatische Entladungen für CMOS-Schaltungen.” 2020.

- Y. Zheng, “Quadraturtakterzeugung für einen Optoelektronischen Empfänger mit 100 GBaud.” 2020.

2019

- J. Brand, “Entwurf und Aufbau eines klirrarmen Sinusgenerators für das Fachpraktikum Schaltungstechnik.” 2019.

- S. Dang, “5-6 GHz 0.25 µm SiGe BiCMOS PA Design.” 2019.

- C. Gantner, “Prototyp-Entwicklung eines On-Chip-Raman-Sensorik-Systems.” 2019.

- P. Hengel, “Portierung eines Entwurfs eines analogen 4-zu-1 Multiplexers in eine 130 nm BiCMOS Technologie.” 2019.

- L. Meyer, “Untersuchung von Schaltungstopologien für analoge Multiplexer.” 2019.

- N. Miller, “Steuerung einer FPGA-basierten Messumgebung.” 2019.

- C. Schweikert, “Untersuchung von reichweitereduzierenden Effekten eines kohärent arbeitenden Laserentfernungsmesssystems.” 2019.

- I. R. Supa Stölben, “Integrierte Wellenleiter-Fotodiode basierend auf laserkristallisierten Germaniumschichten.” 2019.

- L. Trommer, “Implementierung einer Ansteuerung für einen schnellen Digital-Analog-Umsetzer mit 128 GSa/s Umsetzungsrate.” 2019.

- V. Veeramalai, “Layout and Analysis of a 4-to-1 Analog Multiplexer in a 130nm SiGe BiCMOS Technology.” 2019.

- Y. Wang, “Charakterisierung und Optimierung von Gitterkoppler-Arrays mit Rückseitenspiegeln.” 2019.

- M. Wittlinger, “Untersuchung der Schaltungstopologie eines sparsamen Mischsignalneurons.” 2019.

- X. Zhong, “Layout Parasitics Study of a Track-and-Hold Amplifier with Switched Emitter Follower.” 2019.

2018

- T. Agacdograyan, “Entwicklung eines logarithmischen Verstärkers mit mehr als 80 dB Dynamikumfang,” 2018.

- W. Allow, “Integrierter polarisationsteilender Gitterkoppler mit festem Glasfaseranschluss.” 2018.

- T. Ağaçdoğrayan, “Entwicklung eines logarithmischen Verstärkers mit mehr als 80 dB Dynamikumfang.” 2018.

- J. Finkbeiner, “Simulation von Sub-Wellenlängen-Wellenleitern.” 2018.

- M. Hüttel, “Entwurf eines analogen 4:1-Multiplexers mit sehr hoher Bandbreite in einer 130 nm BiCMOS Technologie,” 2018.

- M. Hüttel, “Entwurf eines analogen 4:1-Multiplexers mit sehr hoher Bandbreite in einer 130 nm BiCMOS Technologie.” 2018.

- L. Jiang, “Design and Implementation of a DRP Component for Multi-Input and Multi-Output MMCM of Xilinx 7 Series and Virtex-6 FPGA,” 2018.

- V. K. Kalyanasundaram, “Design of a High-Speed Clock Regeneration Circuit for a 128 GS/s Analog Demultiplexer,” 2018.

- L. Kauke, “Auslegung von Multimoden-Interferometern für die spektrale Analyse optischer Signale,” 2018.

- S. Khalid, “Physikalischer Entwurf eines schnellen CMOS-Rechenwerks für einen Analog-Digital-Umsetzer,” 2018.

- D. Krüger, “Operationsverstärkerschaltung zur Messung von Strömen im Nanoampere-Bereich,” 2018.

- D. Krüger, “Operationsverstärkerschaltung zur Messung von Strömen im Nanoampere-Bereich.” 2018.

- Y. Li, “Extrem rauscharmer Ladungsverstärker für schnellste Staubteilchen,” 2018.

- Y. Li, “Extrem rauscharmer Ladungsverstärker für schnellste Staubteilchen.” 2018.

- M. Lippoldt, “Entwurf und Optimierung eines rücksetzbaren, strahlungsharten Taktteilers mit Fehlerdetektion und zugehörigen Komponenten.” 2018.

- M. Lippoldt, “Entwurf und Optimierung eines rücksetzbaren, strahlungsharten Taktteilers mit Fehlerdetektion und zugehörigen Komponenten,” 2018.

- T. Polder, “Integration von Laserdioden in integriert-optische Systeme,” 2018.

- K. J. Roberts, “Entwurf einer FPGA-basierten Messumgebung für Chips mit hochbitratiger paralleler Schnittstelle.” 2018.

- T. Schüssler, “Redesign of an LNA for 5 GHz to 6 GHz Band,” 2018.

- T. Schüssler, “Redesign of an LNA for 5 GHz to 6 GHz Band.” 2018.

- N. Sesitashvili, “Untersuchung und Entwurf von Schnittstellen und Schutzkonzepten gegen elektrostatische Entladungen für 28-nm-CMOS-Schaltungen,” 2018.

- N. Sesitashvili, “Untersuchung und Entwurf von Schnittstellen und Schutzkonzepten gegen elektrostatische Entladungen für 28-nm-CMOS-Schaltungen.” 2018.

- P. Xiao, “Optimierung einer automatischen Verstärkungsregelung in einer 130 nm CMOS-Technologie.” 2018.

- P. Xiao, “Optimierung einer automatischen Verstärkungsregelung in einer 130 nm CMOS-Technologie,” 2018.

- R. Zhou, “Evaluation eines echtzeitfähigen digitalen Korrekturverfahrens für einen Analog/Digital-Umsetzer,” 2018.

- R. Zhou, “Evaluation eines echtzeitfähigen digitalen Korrekturverfahrens für einen Analog/Digital-Umsetzer.” 2018.

- Ö. Özturk, “Charakterisierung von Polymer-Deckschichten in integrierten Silizium-Hybrid-Modulatoren,” 2018.

2017

- S. Dang, “Vergleichsstudie von Schaltungskonzepten für einen analogen 2:1 Multiplexer in einer SiGe BiCMOS-Technologie.” 2017.

- F. Dreyer, “Laserkristallisation von Germanium für Infrarot-Fotodioden.” 2017.

- C. J. Fuchs, “Rauschuntersuchungen und Fehleranalyse eines integrierten 27MHz GmC Bandpassfilters.” 2017.

- M. Haug, “Realisierung einer kompakten optischen Faserschnittstelle für die integrierte Photonik.” 2017.

- M. Heckmann, “Entwurf einer Ansteuerschaltung zur stabilen Arbeitspunkteinstellung optischer Modulatoren.” 2017.

- J. Huang, “Entwurf einer Referenzspannungsregelung für einen Analog/Digital-Umsetzer,” 2017.

- L. Jiang, “Design of a DRP Component for MMCM of Xilinx 7 Series and Virtex-6 FPGA.” 2017.

- S. Khanof, “Design and Layout of Fast, Bipolar CML Logic Gates in a 130 nm BiCMOS technology.” 2017.

- L. Kramer, “Entwicklung und Aufbau eines Gerätes zur Synchronisation von Zeit-/Digitalumsetzern.” 2017.

- M. Maler, “Studie zu einem rauscharmen Ladungsverstärker mit anpassbarer Eingangsstufe.” 2017.

- S. Oesterwind, “Entwicklung eines Zeit-/Digitalumsetzers auf FPGA-Basis.” 2017.

- T. Petzold, “Entwurf eines schnellen CMOS-Rechenwerkes für einen Analog/Digital-Umsetzer.” 2017.

- C. Raichle, “Bandbreitenoptimierung von Gitterkopplern.” 2017.

- A. Sakr, “Circuit for Calibration of a Fast Digital-to-Analog Converter in a 28 nm Technology.” 2017.

- R. Sweidan, “Realisierung eines integriert-optischen Sensors zur selektiven Blei-Ionen-Detektion.” 2017.

- S. Weber, “Entwurf eines limitierenden Verstärkers für 27 MHz in einer 130 nm CMOS Technologie.” 2017.

- M. Wittlinger, “Entwurf eines breitbandigen linearen Verstärkers mit einstellbarem Frequenzgang.” 2017.

- R. Ziegler, “Entwurf analoger Schaltungskomponenten für einen Faltungs- und Interpolations-Analog/Digital-Umsetzer.” 2017.

Weitere Informationen zu Bachelor-, Forschungs- und Masterarbeiten

Markus Grözing

Dr.-Ing.Arbeitsgruppenleiter IC-Entwurf