Der stetige Anstieg des globalen Datenverkehrs treibt die Datenraten in optischen Übertragungssystemen auf über 1 Tbit/s pro Trägerwellenlänge. Digital-Analog-Umsetzer (DAU) in den Sendesystemen sind kritische Komponenten, an welche hohe Anforderungen gestellt werden. So sind Umsetzungsraten von 100 GS/s und höher erforderlich. Zur monolithischen Integration mit den digitalen Signalprozessoren sind CMOS-Realisierungen dabei unabdingbar.

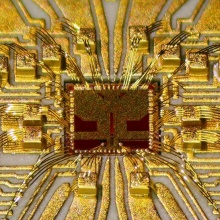

In diesem Projekt wird erstmals die Integration zweier 8-Bit-DAU und eines analogen Multiplexers (AMUX) auf einem einzigen Chip in einer 28-nm-CMOS-Technologie (FD-SOI) bei Umsetzungsraten von über 100 GS/s realisiert. Ein integrierter Speicher (SRAM) mit einer Speichergröße von 256 kB, der zyklisch ausgelesen wird, vervollständigt das System zu einem universellen Arbiträrsignalgenerator (AWG). Dieser besteht aus insgesamt über 14 Millionen Transistoren. Allgemein können durch einen AMUX Umsetzungsraten und Bandbreiten von DAUn in etablierten CMOS-Technologien gesteigert werden, was neben der reinen Weiterentwicklung der Technologie einen zweiten Pfad zur Performance-Steigerung eröffnet. Der AWG ist für den Einsatz in experimentellen, optischen Übertragungsstrecken sowie für verschiedenste Laborexperimente, welche sehr schnelle AWG benötigen, entwickelt.

Breitbandige, pulsamplitudenmodulierte (PAM) Signale bis zur Nyquist-Frequenz werden bis zu einer Umsetzungsrate von 108 GS/s (PAM-2) und Datenraten bis zu 240 Gbit/s (80 GS/s, PAM-8) demonstriert. Bei 100 GS/s wird ein PAM-4-Signal gezeigt. Des Weiteren kann der AWG für Anwendungen mit Überabtastung und Pulsformung bei geringeren Symbolraten mit Umsetzungsraten bis zu 118 GS/s eingesetzt werden.

Zuletzt geht aus diesem Projekt ein Vorverzerrungsverfahren im Zeitbereich einschließlich Systemidentifikationsverfahren hervor, das deterministische, lineare, periodisch zeitvariante Effekte (LPTV) berücksichtigt.

Publikationen

2024

- D. Widmann, T. Tannert, X.-Q. Du, T. Veigel, M. Grözing, and M. Berroth, “A Time-Interleaved Digital-to-Analog Converter up to 118 GS/s With Integrated Analog Multiplexer in 28-nm FD-SOI CMOS Technology,” IEEE Journal of Solid State Circuits, vol. 59, pp. 908–922, 2024.

2023

- D. Widmann, M. Grözing, and M. Berroth, “Digital Time-Domain Predistortion of Linear Periodically Time-Varying Effects and Its Application to a 100-GS/s Time-Interleaved CMOS DAC,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 70, pp. 5098–5109, 2023.

- D. Widmann, T. Tannert, M. Grözing, and M. Berroth, “Analog Multiplexer for Performance Enhancement of Digital-to-Analog Converters and Experimental 2-to-1 Time Interleaving in 28-nm FD-SOI CMOS,” IEEE Solid-State Circuits Letters, vol. 6, pp. 277–280, 2023.

2022

- D. Widmann, R. Nägele, M. Grözing, and M. Berroth, “Mixed-Signal Integrated Circuit for Direct Raised-Cosine Filter Waveform Synthesis of Digital Signals Up to 24 GS/s in 22 nm FD-SOI CMOS Technology,” in IEEE International Symposium on Circuits and Systems (ISCAS), 2022, p. paper ID 1248.

- D. Widmann, T. Tannert, X.-Q. Du, M. Grözing, and M. Berroth, “Multi-Phase Clock Path Circuit up to 57 GHz Including 5 bit Programmable Phase Interpolators for Time-Interleaved Broadband Data Converters in a 28 nm FD-SOI CMOS Technology,” in European Microwave Integrated Circuits Conference (EuMIC), 2022, pp. 177–180.

2018

- D. Widmann, M. Gözing, and M. Berroth, “High-Speed Serializer for a 64 GS s-1 Digital-to-Analog Converter in a 28 nm Fully-Depleted Silicon-on-Insulator CMOS Technology,” Advances in Radio Science, vol. 16, pp. 99–108, 2018.

2017

- T. Veigel, S. Brandl, and M. Grözing, “Speicher mit 1 Tbit/s Lesedurchsatz für einen sehr schnellen Arbiträrsignalgenerator in einer 28 nm FDSOI-CMOS-Technologie,” in Kleinheubacher Tagung, U.R.S.I. Landesausschuss in der Bundesrepublik Deutschland e.V, Miltenberg, Germany, 2017, pp. KH2017–Di.

- D. Widmann, M. Grözing, and M. Berroth, “A differential 19 channel 64 Gbit/s 16:1 multiplexer including a clock network in a 28 nm CMOS Fully-Depleted Silicon-on-Insulator technology,” in Kleinheubacher Tagung, U.R.S.I. Landesausschuss in der Bundesrepublik Deutschland e.V, Miltenberg, Germany, 2017, pp. KH2017–Di.

Weiterführende Informationen

- DFG-Projekt

Schnellste Digital-Analog-Umsetzer mit geringer Verlustleistung in FDSOI-CMOS-Technologie für die ultra-breitbandige Datenübertragung - Erster 100 GS/s integrierter CMOS Digital-Analog-Umsetzer

Ansprechpartner

Markus Grözing

Dr.-Ing.Arbeitsgruppenleiter IC-Entwurf