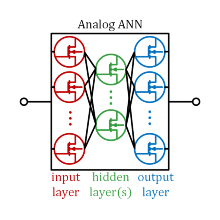

Die enorme Leistungsfähigkeit künstlicher Intelligenz bei unterschiedlichen Problemstellungen führt zu deren Einzug in immer mehr Anwendungen und löste insbesondere mit der Einführung von ChatGPT einem regelrechten Boom aus. Derartige Systeme basieren auf künstlichen neuronalen Netzen für deren Inferenz im Wesentlichen die zwei arithmetischen Operationen Multiplikation und Addition billionenfach berechnet werden.

In konventionellen digitalen Rechenwerken werden für das einfache Multiplizieren zweier Zahlen in sogenannten Feldmultiplizierern viele hundert MOSFETs verwendet und für jede Rechnung umgeladen, wodurch beim Rechnen viel Energie aufgewendet wird. Hier setzt das neue analogen Rechenschaltungskonzept des INT an, welches im Rahmen des vom BMBF geförderten AI-NET Forschungsprojekt entwickelt wurde. Der analoge Zweiquadranten-Multiplizierer kommt mit nur zwei Feldeffektransistoren aus. Durch diese fließt für nur einen sehr kurzen Augenblick Strom, wobei das Multiplikationsergebnis, abgebildet als elektrische Ladung, berechnet wird. Für die Addition wird sogar gar kein zusätzliches Bauelement benötigt, da hier das physikalische Prinzip der Kirchhoffschen Knotenregel ausgenutzt wird. Dadurch ergibt sich ein sehr großes Effizienzsteigerungspotential. Rechenwerke für KI-Anwendungen auf Computerchips in Rechenzentren und Smartphones sowie Sende- und Empfängerschaltungen für die optische Datenübertragung könnten somit deutlich kleiner und energieeffizienter werden. Die bisherigen Untersuchungen deuten darauf hin, dass eine analoge Multiplikation mit der neuen Technik des INT etwa 100-fach energieeffizienter ist als eine bereits stark reduzierte und optimierte digitale FP4-Multiplikation auf der neuesten Nvidia KI-Beschleuniger-Generation (GPU Blackwell GB200).

Im Laufe des Projekts sind zwei ASICs in einer 22 nm FDSOI CMOS Technologie entstanden, welche die grundlegende Funktionalität der analogen Rechenzellen als auch die niedrige Energieaufnahme durch messtechnische Charakterisierung bestätigen.

Die Abbildung zeigt den zweiten entworfenen ASIC auf dem mehrere neuronale Schichten, basierend auf den analogen Rechenzellen, implementiert sind.

Publikationen

2024

- J. Finkbeiner, R. Nägele, M. Grözing, M. Berroth, and G. Rademacher, “Characterization of a Femtojoule Voltage-to-Time Converter with Rectified Linear Unit Characteristic for Analog Neural Network Inference Accelerators,” in IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2024, pp. 253–257.

- J. Finkbeiner, R. Nägele, M. Grözing, M. Berroth, and G. Rademacher, “Ultra-energy-efficient analog multiply-accumulate and rectified linear unit circuit for artificial neural network inference accelerators,” in International Conference on Neuromorphic Computing and Engineering 2024 (ICNCE), 2024.

- R. Nägele, J. Finkbeiner, M. Grözing, M. Berroth, and G. Rademacher, “Characterization of an Analog MAC Cell with Multi-Bit Resolution for AI Inference Accelerators,” in IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), 2024, pp. 243–247.

2023

- R. Nägele, J. Finkbeiner, V. Stadtlander, M. Grözing, and M. Berroth, “Analog Multiply-Accumulate Cell with Multi-Bit Resolution for All-Analog AI Inference Accelerators,” IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 2023, pp. 1–13, 2023.

2022

- J. Finkbeiner, R. Nägele, M. Berroth, and M. Grözing, “Design of an Energy Efficient Voltage-to-Time Converter with Rectified Linear Unit Characteristics for Artificial Neural Networks,” in IEEE International New Circuits and Systems Conference (NEWCAS), 2022, pp. 327–331.

- R. Nägele, J. Finkbeiner, M. Berroth, and M. Grözing, “Design of an Energy Efficient Analog Two-Quadrant Multiplier Cell Operating in Weak Inversion,” in IEEE International New Circuits and Systems Conference (NEWCAS), 2022, pp. 5–9.

Weiterführende Informationen

- Projektseite des Projektträgers

Automatisierte Telekommunikationsinfrastruktur mit intelligenten autonomen Systemen - Projektseite des internationalen Konsortiums

Accelerating digital transformation in Europe by Intelligent NETwork automation - Pressemitteilung des BMBF

Karliczek: Leistungsfähige Netzinfrastruktur ist zentrales Nervensystem für Wirtschaft und Gesellschaft - Pressemitteilung des INT

Forscher des INT erhalten Zukunftpreis für analoge KI-Beschleunigung - Pressemitteilung der Ewald Marquardt Stiftung

Private Stiftung Ewald Marquardt verleiht Zukunftspreis 2023

Kontakt

Jakob Finkbeiner

M. Sc.Wissenschaftlicher Mitarbeiter

Raphael Nägele

M. Sc.Wissenschaftlicher Mitarbeiter