The technological aim of the TARANTO EU project is to develop heterojunction bipolar transistors (HBTs) with a maximum oscillation frequency of fmax = 600 GHz. These HBTs are embedded into modern high integration CMOS processes like 130 nm or 90 nm from Infineon and 55 nm or 28 nm from ST Microelectronics. IHP is working on maximum oscillation frequencies of 700 GHz.

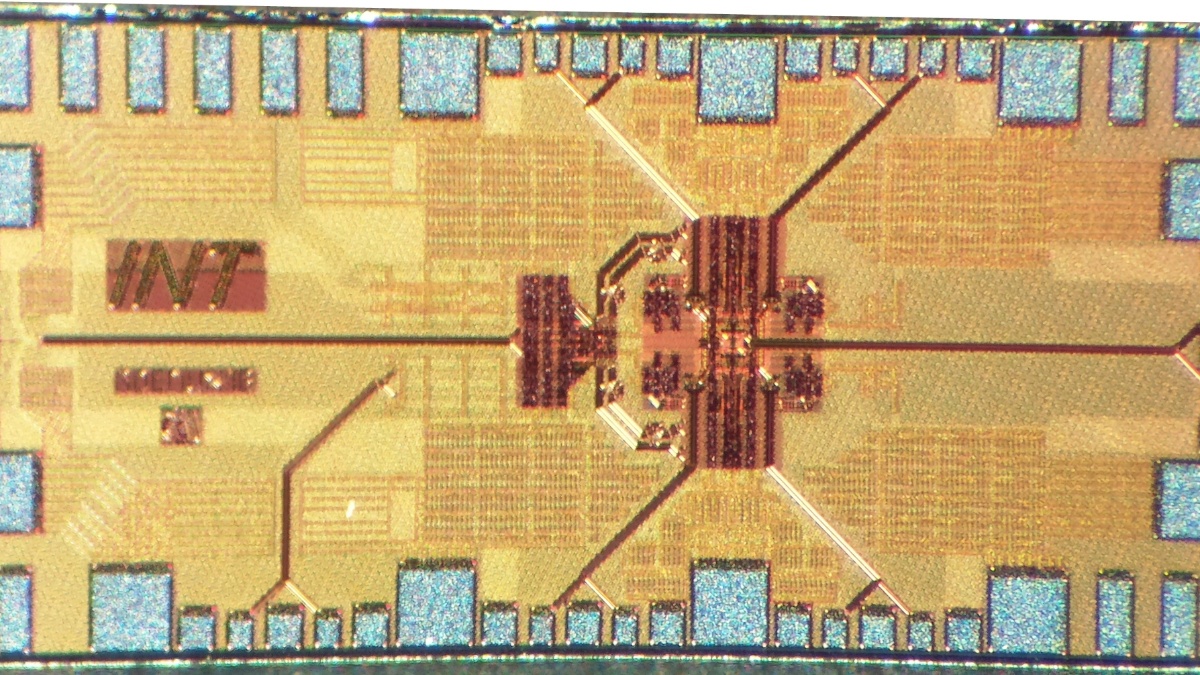

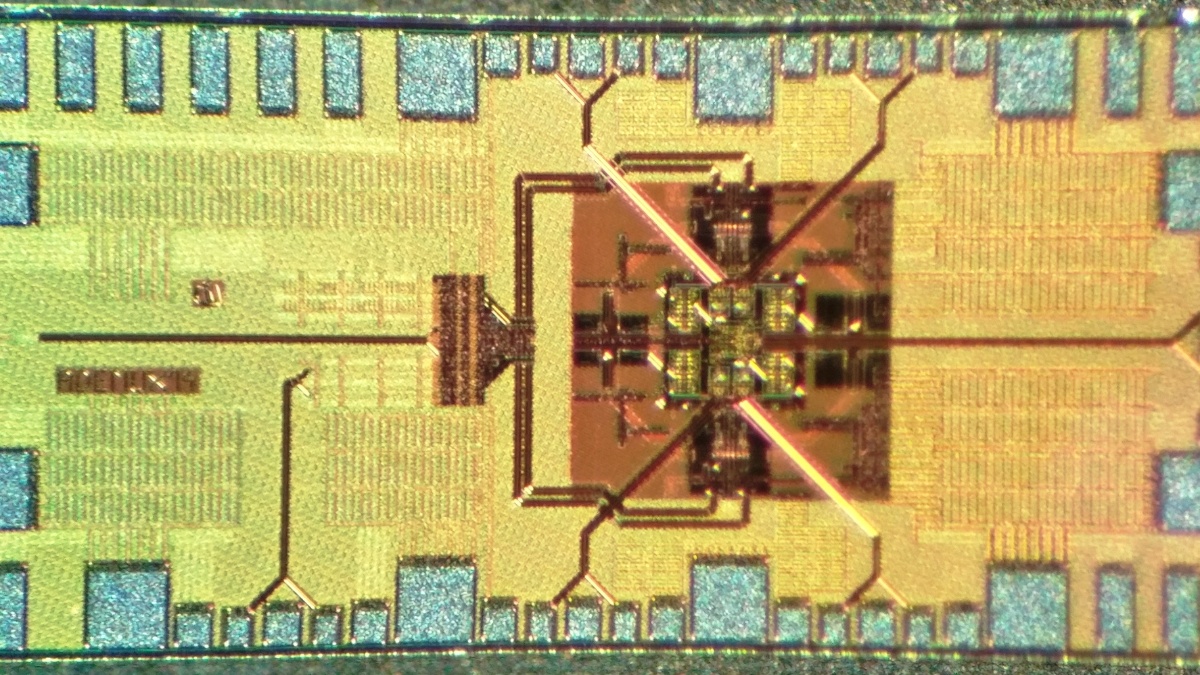

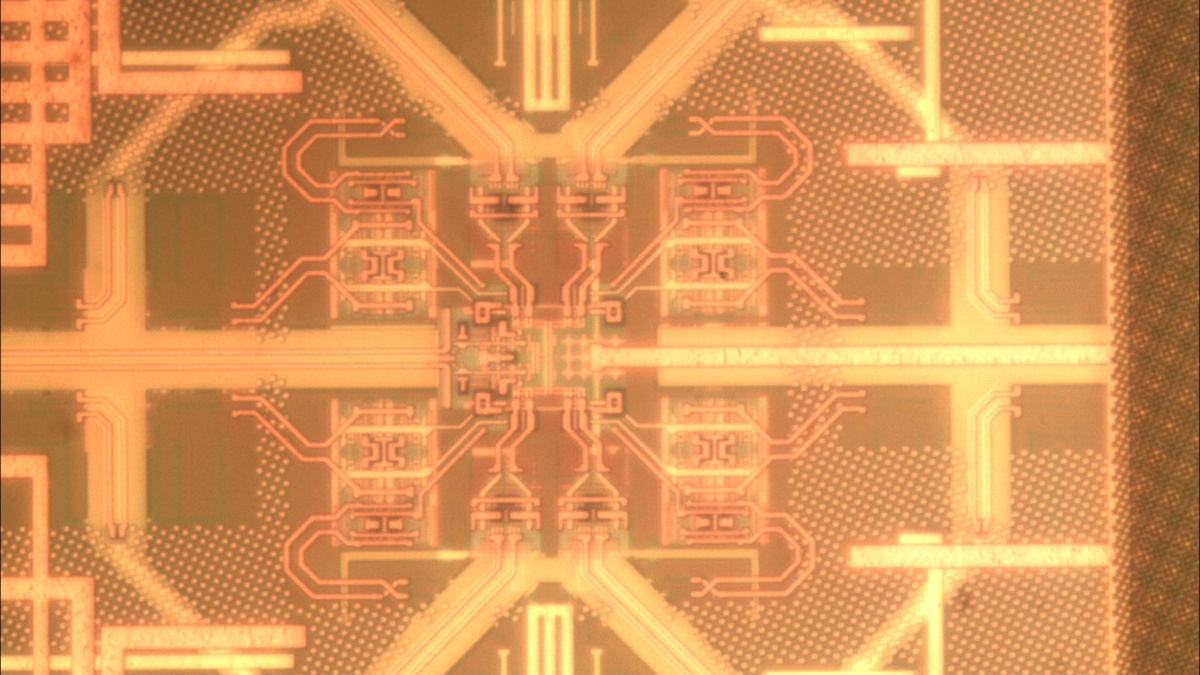

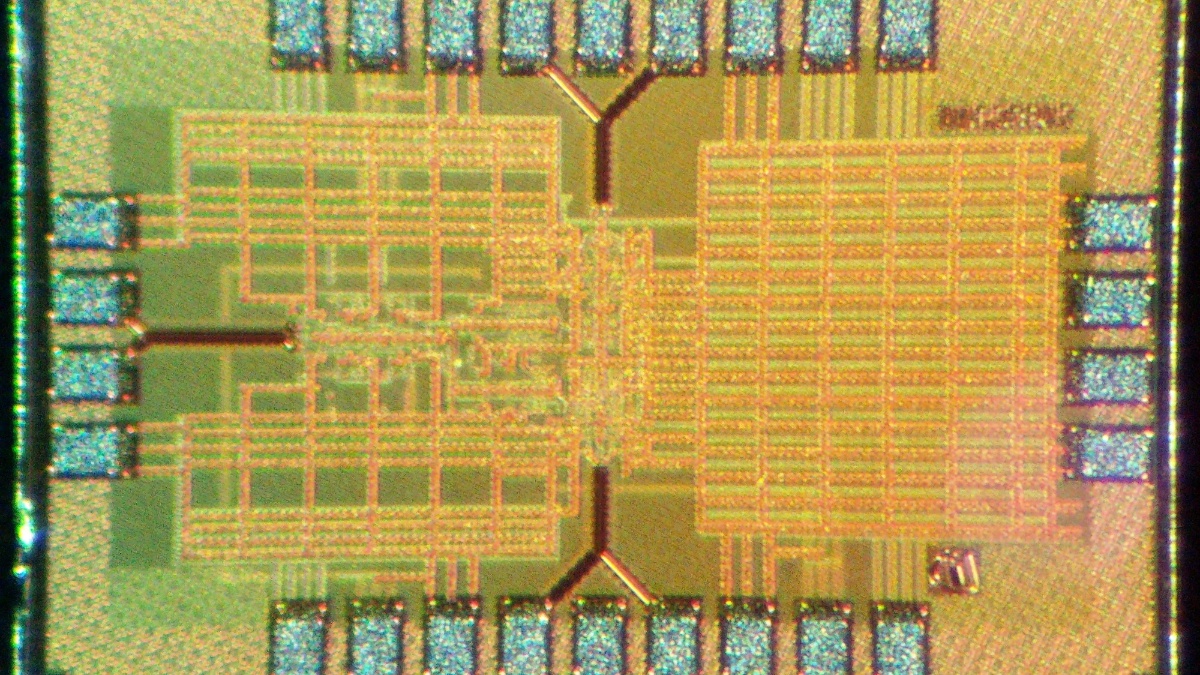

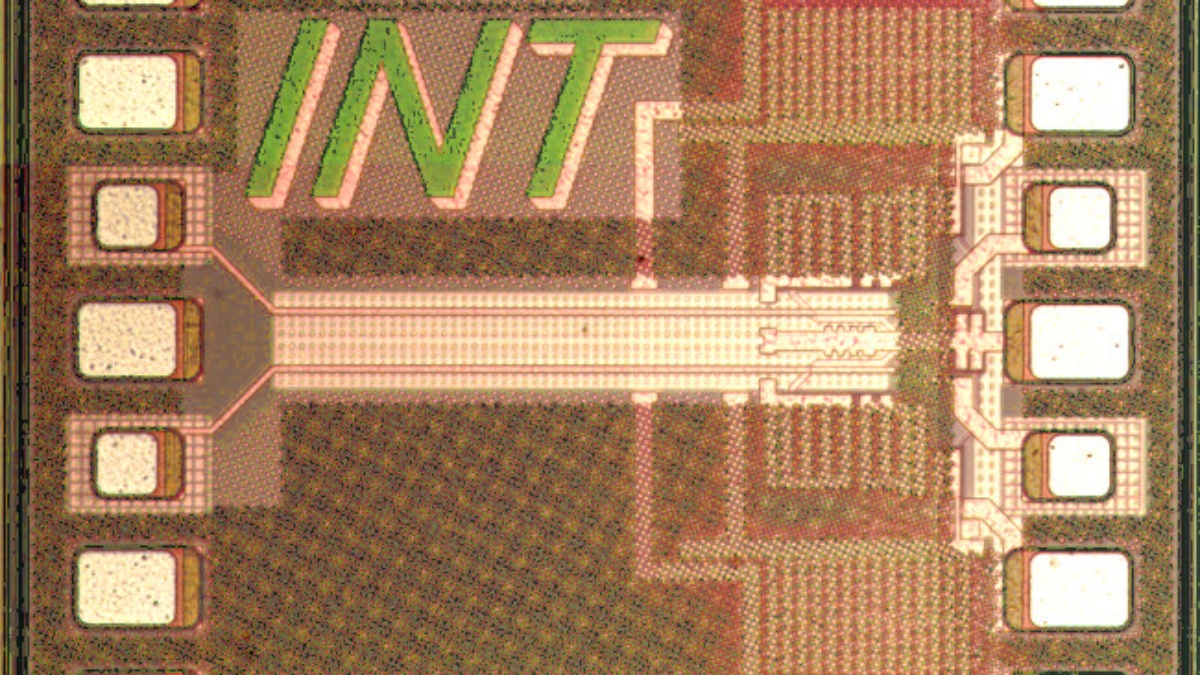

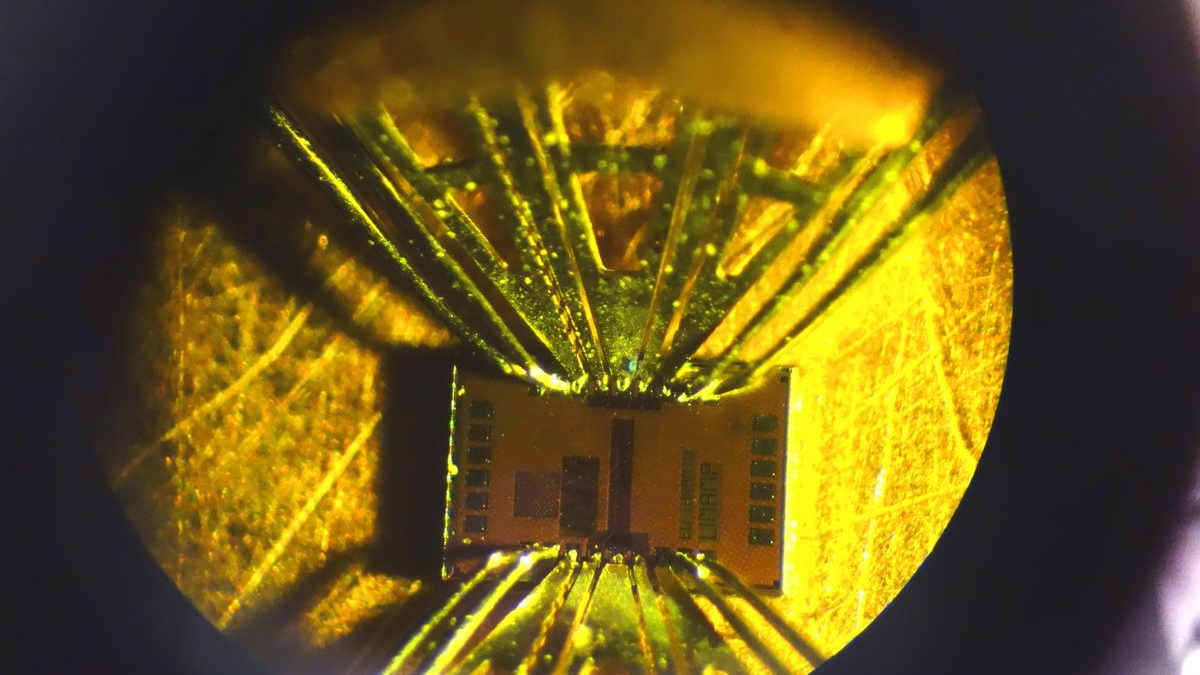

Within the TARANTO project, INT is responsible for design, layout and characterization of ultra-fast front-end input circuits for analog-to-digital converters. We use modern high-speed BiCMOS processes of the technology nodes of 130 nm and 90 nm. To reach sampling rates beyond 100 GS/s with high bandwidth, we apply the principle of fourfold synchronous time interleaving. The principle is illustrated in the following figure. A clock divider generates a four-phase clock that controls four time-interleaved track-and-hold circuits. We use two different approaches for the design of the track-and-hold circuits: voltage mode, where the sampled input voltage is stored on a hold-capacitor and current mode, where the input current accumulates a charge on a resettable hold-capacitor.

Measurement results for a single current-mode track-and-hold chip have been published at IEEE BCICTS 2018 conference. The circuit exhibits a 1-dB-bandwidth of 40 GHz and shows an effective resolution (ENOB) of 5 to 6.4 up to the second Nyquist frequency.

Further chips for single critical components, like track-and-hold circuits and broadband amplifiers, as well as complete 1-to-4 interleaver-ICs at more than 100 GS/s have also been designed and fabricated.

Publications

2022

- P. Thomas, J. Finkbeiner, M. Grözing, and M. Berroth, “Time-Interleaved Switched Emitter Followers to Extend Front-End Sampling Rates up to 200 GS/s,” IEEE Journal of Solid State Circuits, pp. 1–12, 2022.

2021

- M. Grözing, X.-Q. Du, P. Thomas, and M. Berroth, “High-Bandwidth Analog-to-Digital-Converter Front-Ends in SiGe-BiCMOS Technology,” in Workshop WFC - Enabling technologies for efficient ultra-high speed wireless communication systems towards 100 Gb/s, IEEE International Microwave Symposium (IMS), 2021.

- T. Tannert, M. Grözing, and M. Berroth, “Quadrature Clock Generation Circuit for Time Interleaved Data Converters,” in Kleinheubacher Tagung, U.R.S.I. Landesausschuss in der Bundesrepublik Deutschland e.V, 2021, pp. 1–4.

- P. Thomas, M. Grözing, and M. Berroth, “64-GS/s 6-Bit Track-and-Hold Circuit with More Than 61 GHz Bandwidth at 1.0 Vpp Input Voltage Swing in 90-nm SiGe BiCMOS Technology,” in IEEE International Symposium on Circuits and Systems (ISCAS), 2021, pp. 1–4.

- P. Thomas, T. Tannert, M. Grözing, M. Berroth, Q. Hu, and F. Buchali, “1-to-4 Analog Demultiplexer with up to 128 GS/s for Interleaving of Bandwidth-Limited Digitizers in Wireline and Optical Receivers,” IEEE Journal of Solid State Circuits, vol. 56, pp. 2611–2623, 2021.

- P. Thomas, T. Tannert, M. Grözing, X.-Q. Du, and M. Berroth, “A 1-to-4 SiGe BiCMOS Analog Demultiplexer Sampling Front-End for a 116 GBaud-Receiver,” in European Microwave Integrated Circuits Conference (EuMIC), 2021, pp. 121–124.

2020

- F. Buchali, X.-Q. Du, K. Schuh, S. T. Le, M. Grözing, and M. Berroth, “A SiGe HBT BiCMOS 1-to-4 ADC frontend enabling low bandwidth digitization of 100 GBaud PAM4 data,” Journal of Lightwave Technology, vol. 38, pp. 150–158, 2020.

- S. T. Le, K. Schuh, F. Buchali, X.-Q. Du, M. Grözing, M. Berroth, L. Schmalen, and H. Bülow, “Single Sideband Transmission Employing a 1-to-4 ADC Frontend and Parallel Digitization, invited paper,” Journal of Lightwave Technology, vol. 38, pp. 3125–3134, 2020.

- P. Thomas, M. Grözing, and M. Berroth, “32-GS/s SiGe Track-and-Hold Amplifier with 58-GHz Bandwidth and -64-dBc to -29-dBc HD3,” in IEEE International Conference on Electronics Circuits and Systems (ICECS), 2020, pp. 1–4.

- P. Thomas, T. Tannert, M. Grözing, and M. Berroth, “128-GS/s 1-to-4 SiGe Analog Demultiplexer with 36-GHz Bandwidth for 6-bit Data Converters,” in IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), 2020, p. pp. 1––4.

2019

- X.-Q. Du, M. Grözing, A. Uhl, S. Park, F. Buchali, K. Schuh, S. T. Le, and M. Berroth, “A 112-GS/s 1-to-4 ADC front-end with more than 35-dBc SFDR and 28-dB SNDR up to 43-GHz in 130-nm SiGe BiCMOS,” in IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Boston, MA, USA, 2019, pp. 215–218.

- M. Grözing, X.-Q. Du, P. Thomas, T. Tannert, M. Berroth, F. Centurelli, P. Tommasino, A. Trifiletti, M. Collisi, M. Möller, H. Hettrich, A. Bielik, R. Schmid, K. Schuh, and F. Buchali, “D/A and A/D Conversion Key ICs for Broadband Communications,” presented at EuMIC/TARANTO Workshop Recent Advances in SiGe BiCMOS: Technologies, Modelling and Circuits for 5G, radar and imaging, Paris, France, 2019.

2018

- X.-Q. Du, M. Grözing, and M. Berroth, “A 25.6-GS/s 40-GHz 1-dB BW Current-Mode Track-and-Hold Circuit with more than 5-ENOB,” in IEEE 2 BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium (BCICTS), San Diego, CA, USA, 2018, pp. 56–59.

Further information

- CORDIS EU research results

TowARds Advanced bicmos NanoTechnology platforms for rf and thz applicatiOns - ECSEL Joint Undertaking

Electronic Components and Systems for European Leadership - TARANTO

Contact

Markus Grözing

Dr.-Ing.Group Leader Integrated Circuits