Design of an Energy Efficient Analog Two-Quadrant Multiplier Cell Operating in Weak Inversion

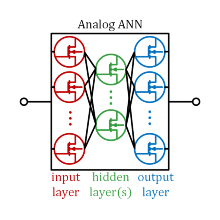

Analog low precision arithmetic circuits offer a significantly higher energy efficiency than their digital counterparts which makes them ideally suited for low precision neuromorphic processing circuits. Therefore an analog two-quadrant multiplier cell consisting of only two MOSFETs with multi-bit resolution is presented. It operates in weak inversion with the backgate used as multiplicator input consuming less than 1 fJ per operation. A 22 nm FD-SOI CMOS technology is used for simulations.

About the IC Group of the Institute of Electrical and Optical Communications Engineering

The IC group of the Institute of Electrical and Optical Communications (INT) is focused in the design of application specific integrated circuits (ASICs) for ultra-broadband optical links, mobile communications, wireless and sensors. INT has more than 20 years of expertise in the design of fast and precise mixed-signal circuits in CMOS, bipolar and BiCMOS technologies in the frequency range from 1 Hz to 100 GHz.