# 4 Technische Beschreibung

## 4.1 Einleitung

Alle optischen und elektrischen Kanäle weisen Dispersionseffekte auf, welche sich insbesondere bei der Realisierung mit kostengünstigen Standardkomponenten und -Materialien verstärkt bemerkbar machen. Dies führt zum "Zerfließen" der binären Datensymbole bei der seriellen Hochgeschwindigkeits-Datenübertragung. Die durch die Dispersion verursachte Intersymbolinterferenz nimmt mit der Datenrate und mit der Kanallänge zu. Ab einer bestimmten Übertragungslänge und Datenrate ist eine rein binäre Entscheidung der Datensymbole im Empfänger daher nicht mehr möglich. Kostengünstige elektronische Entzerrer können die Kanalverzerrungen bis zu einem gewissen Grad ausgleichen und sind daher ein Thema aktueller Forschung.

### 4.2 Stand der Technik

Es gibt zwei grundsätzliche Möglichkeiten, den Kanalverzerrungen elektronisch entgegenzuwirken: Die Vorverzerrung des Signals im Sender und die Nachverzerrung des Signals im Empfänger [1, 2]. Am weitesten verbreitet ist die Vorverzerrung des Signals im Sender mittels eines getakteten Filters mit finiter Impulsantwort (engl. *finite impulse response, FIR*) [3]. Dieses Verfahren ist mit einfachen binären Verzögerungsgliedern (Flip-Flops) und gewichteten Analogaddierern in der Leitungstreiberstufe relativ einfach umzusetzen und wird oft als *Preemphasis* bezeichnet. Zusätzlich wird im Empfänger häufig ein entscheidungsrückgekoppeltes Filter (engl. *decision feedback equalizer, DFE*) eingesetzt [4]. Mitunter wird im Empfänger vor den DFE noch ein zeitkontinuierlicher Peakingverstärker geschaltet [5].

Die Vorverzerrung im Sender ist zwar relativ einfach umzusetzen, hat aber zwei entscheidende Nachteile. Erstes ist das Wissen um die Kanaleigenschaften, welches zur Einstellung der Entzerrerkoeffizienten notwendig ist, auf der Sendeseite schwieriger zu beschaffen als auf der Empfängerseite. Im Empfänger kann der Kanal z.B. mittels bekannter Initialisierungssequenzen charakterisiert werden, und die Entzerrerkoeffizienten können lokal eingestellt werden. Bei einem zeitveränderlichen Kanal<sup>3</sup> können die Koeffizienten auch über die Messung von Fehlersignalen<sup>4</sup> mit Hilfe von fehlerminimierenden Algorithmen<sup>5</sup> nachgeführt werden. Für die Vorverzerrung im Sender ist hingegen bei zeitveränderlichen Kanälen ein Rückkanal notwendig, damit die gemessenen Kanaleigenschaften vom Empfänger an den Sender übermittelt werden können. Dies bringt insbesondere bei Übertragungsstrecken, bei denen Sender und Empfänger von verschiedenen Herstellern

<sup>3</sup> Zeitveränderlich ist z.B. die Polarisationsmodendispersion (PMD) in Glasfasern. Zeitveränderlich ist auch der DRAM-Speicherbus im PC, bei dem die Möglichkeit bestehen soll, ein vorhandenes DRAM-Speichermodul gegen ein neues eines anderen Herstellers auszuwechseln. Nach dem Austausch müssen die Sender und

Empfänger auf beiden Seiten mit dem nun veränderten Kanal zurechtkommen.

<sup>&</sup>lt;sup>4</sup> Differenz des Signals vor und nach dem Entscheider. Bei idealer Entzerrung ist das Auge des empfangenen Signals hinter dem Empfangsfilter und vor dem Entscheider maximal geöffnet, und das Fehlersignal wird minimal.

<sup>&</sup>lt;sup>5</sup> z.B. LMS- (*least mean square*) Algorithmus.

stammen (z.B. beim DRAM-Speicherbus) erhebliche Probleme mit sich, da sich die verschiedenen Hersteller über noch mehr Details der Sender und Empfänger einigen müssen. Der zweite Nachteil der Vorverzerrung ist, dass die hochfrequenten Signalanteile zum Ausgleich des dispersionsbehafteten Kanals schon im Sender angehoben werden. Dadurch wird die kapazitive Kopplung auf Nachbarkanäle, welche ein Hochpassverhalten aufweist, verstärkt. Die Signalintegrität wird also durch verstärktes Übersprechens verschlechtert.

Die Entzerrung im Empfänger mittels eines entscheidungsrückgekoppelten Filters (DFE) setzt voraus, dass die Impulsantwort des Kanals eine steile ansteigende Flanke aufweist, weil das DFE-Filter nur Impulsnachläufer unterdrücken kann und keine Impulsvorläufer. Daher werden direkt vor das DFE-Filter oft die oben erwähnten Peakingverstärker geschaltet. Ansonsten muss das Signal zur Unterdrückung der Impulsvorläufer zusätzlich schon im Sender vorverzerrt werden, mit all den oben beschriebenen Nachteilen.

Für optische Systeme werden im Empfänger häufig relativ lange FIR-Filter (sog. Transversalentzerrer) eingesetzt [6]. Diese werden meist als flächen- und leistungsintensive gepufferte LC-Verzögerungsleitung umgesetzt. Neben dem hohen Flächenverbrauch besteht ein entscheidender Nachteil der LC-Verzögerungsleitungen darin, dass die Datenrate über die Verzögerungselemente fest eingestellt ist.

Um mit relativ langsamen Schaltungen ohne induktives Peaking hohe Empfangsdatenraten verarbeiten zu können, wurden verschiedene voll-parallel arbeitende abtastende Entzerrerkonzepte vorgeschlagen [7, 8] und jüngst für Datenraten bis 8 Gbit/s demonstriert [9]. Dabei wird ausgenutzt, dass relativ langsam getaktete Folge-Halte-Glieder bei geeignetem Entwurf am Eingang trotzdem eine recht hohe Eingangsbandbreite aufweisen. Bei den voll-parallelen Entzerrern ist der Grad des zu realisierenden Filters direkt mit dem Grad der Parallelisierung verknüpft. So ist in [9] für die Umsetzung eines FIR-Filters mit 4 Anzapfungen eine 8-fach parallele Struktur notwendig. Die starke Parallelisierung am seriellen Dateneingang verursacht Probleme beim Layout der parallelen Pfade und bei der präzisen Verteilung des Multiphasentaktes. Außerdem ist eine Erhöhung des Filtergrades zwangsläufig mit einer Erhöhung der Parallelisierung und damit mit einem kompletten Neuentwurf der Takterzeugung und der Filterstruktur verbunden.

In [10] wurde schon 1993 ein Konzept präsentiert, bei welchem die abgetastete Symbolwerte abwechseln in zwei parallele getaktete Verzögerungsketten eingespeist werden, welche dann mit der halben Taktfrequenz betrieben werden. Das Prinzip wurde allerdings damals nur bei einer Datenrate von 40 Mbit/s demonstriert. Dieses Konzept wurde später wieder aufgegriffen [11-13]. Prinzipiell kann mit dieser Struktur ein parallelisiertes FIR-Filter aufgebaut werden, bei welchem der Grad des Filters und der Grad der Parallelisierung unabhängig voneinander ist. Der Nachteil der in [10-13] umgesetzten Filter besteht darin, dass die parallelen Pfade nicht symmetrisch zueinander sind. In den parallelen Pfaden sind zum Zwecke der Synchronisation der Datensymbole jeweils eine unterschiedliche Anzahl von Abtast-bzw. Folge-Halte-Gliedern in Serie geschaltet. Außerdem ist der Taktphasenabstand, mit dem aufeinander folgende Glieder im ersten Abschnitt der Verzögerungsketten angesteuert werden, bei den Filtern mit einem Parallelisierungsgrad größer zwei unterschiedlich groß [11]. Dies führt zu unterschiedlich großen zusätzlichen Verzerrungen in den parallelen Pfaden, welche nicht durch eine Nachjustierung der Entzerrerkoeffizienten kompensiert werden können.

# 4.3 Übertragungskanal

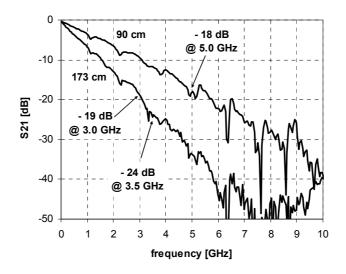

**Abbildung 4.1:** Gemessene Einfügedämpfung  $S_{21}$  einer 90 cm langen und einer 173 langen 50  $\Omega$  Mikrostreifenleitung auf FR4 Leiterplattensubstrat.

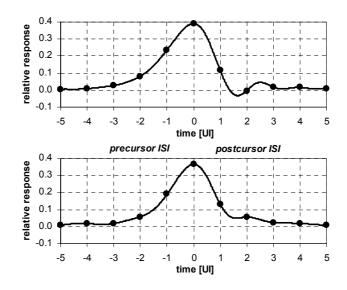

**Abbildung 4.2:** Gemessene Impulsantwort

der 90 cm langen Leitung bei 10 Gbit/s (oben) und der 173 cm langen Leitung bei 6 Gbit/s (unten).

Als Testkanäle werden differenzielle Paare von 50  $\Omega$  Mikrostreifenleitungen auf normalem FR4 Leiterplattensubstrat verwendet. Abbildung 4.1 zeigt die Einfügedämpfung einer 90 cm langen und einer 173 cm langen 50  $\Omega$  Leitung. Die Dämpfung der 90 cm langen Leitung bei der Nyquistfrequenz für eine Übertragung mit 10 Gbit/s ist gleich 18 dB, die entsprechende Dämpfung beträgt 19 dB für die 173 cm lange Leitung bei 6 Gbit/s und 24 dB für die 173 cm lange Leitung bei 7 Gbit/s. In Abbildung 4.2 ist die Antwort der 90 cm bzw. der 173 cm langen Leitung auf ein Einheitssymbol (Symbol mit der Dauer  $T = 1/f_{Bit}$  und der Amplitude eins) für eine Datenrate von 10 Gbit/s bzw. 6 Gbit/s dargestellt. Die Impulsantwort erreicht die Entscheiderschwelle ½ nicht. Außerdem ist die Impulsantwort über ca. 6 Einheitsintervalle verschmiert. Wie aus den Augendiagrammen in Abbildung 4.13 und Abbildung 4.11 deutlich wird, sind dann die Augendiagramme am Ende der Leitungen vollkommen geschlossen. Ein Empfang des Datenstroms mit einem rein binären Empfänger führt zu einer Bitfehlerrate größer als  $10^{-1}$ .

## 4.4 Entzerrerkonzept

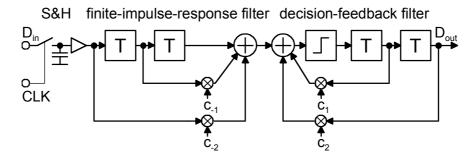

**Abbildung 4.3:** Prinzipielle Struktur des Entzerrungsfilters: Kombination eines FIR-Filters mit einem entscheidungsrückgekoppelten Filter (DFE).

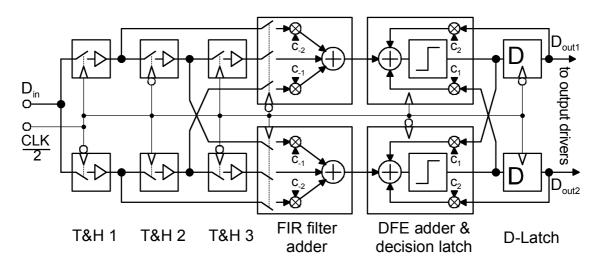

**Abbildung 4.4:** Umsetzung der Filterstruktur in eine symmetrische Halbratenstruktur. Die Struktur wird mit einer Taktfrequenz entsprechend der halben Bitrate am Eingang angesteuert und die entzerrten Daten werden an zwei Ausgängen mit der halben Eingangsdatenrate ausgegeben.

Der hier vorgestellte Entzerrer verwendet ein empfängerseitiges FIR-Filter mit drei Anzapfungen und ein nachfolgendes entscheidungsrückgekoppeltes Filter mit zwei Rückführungen. Als Verzögerungselemente für das FIR-Filter werden einfach Folge-Halte-Glieder (engl. track & hold circuit, T&H) eingesetzt. Es werden weder flächenintensive LC-Elemente oder Verzögerungsleitungen noch irgendwelche anderen zeitkontinuierlichen analogen Verzögerungselemente benötigt. Die Verzögerungszeit zwischen den Filteranzapfungen wird vom datensynchronen Takt vorgegeben, so dass ein voll bitratenflexibler Entwurf entsteht. Es wird eine moderate 2-fache Parallelisierung der Signalverarbeitung gewählt, um die maximale Eingangsdatenrate des Entzerrers zu erhöhen und um die Länge der Verzögerungsketten zu reduzieren.

#### Entwurf der Filterstruktur

Der Ausgangspunkt für den Entwurf der Filterstruktur ist die Impulsantwort im Zeitbereich entsprechend Abbildung 4.2. Die Impulsantwort hat bei den betrachteten Datenraten und Leitungslängen zwei deutlich hervortretende Abtastwerte vor ihrem Maximum (so genannte Impulsvorläufer, engl. precursor intersymbol interference, precursor ISI), welche mit vorauslaufenden Datensymbolen interferieren. Außerdem hat die Impulsantwort zwei deutlich hervortretende Abtastwerte nach ihrem Maximum (so genante Impulsnachläufer, engl. postcursor ISI), welche mit nachlaufenden Datensymbolen interferieren.

Die Impulsvorläufer können effektiv mit einem FIR-Filter mit drei Anzapfungen unterdrückt werden. Einer der drei Koeffizienten ist fest eingestellt und zwei Koeffizienten haben zwar ein festes Vorzeichen, sind aber vom Betrag her einstellbar. Die verbleibenden Impulsnachläufer werden mit einem entscheidungsrückgekoppelten Filter (engl. *decision feedback equalizer*, *DFE*) mit 2 Rückführungen beseitigt. Beide Koeffizienten des entscheidungsrückgekoppelten Filters sind sowohl im Vorzeichen wie im Betrag einstellbar. Die gesamte logische Struktur des zeitdiskreten Filters ist in Abbildung 4.3 dargestellt.

#### Halbraten-Signalverarbeitung

Die Einheitsverzögerungen für das FIR-Filter werden mittels Folge-Halte-Gliedern realisiert. Bei einem Filterkonzept, das mit der vollen Taktfrequenz arbeitet, werden zwei kaskadierte Folge-Halte-Glieder in einer Master-Slave-Anordnung benötigt, um eine Einheitsverzögerung  $T=1/f_{\rm Bit}$  zu realisieren. In solch einer Anordnung steht dann nur 50% des Einheitszeitintervalls T zum Folgen zur Verfügung. Daher werden bei einer Vollraten-Signalverarbeitung 6 kaskadierte Folge-Halte-Glieder für das FIR-Filter mit drei Anzapfungen benötigt, da das Abtast-Halte-Glied am Eingang auch durch zwei kaskadierte Folge-Halte-Glieder realisiert wird.

Die Bandbreite der Folge-Halte-Glieder in der Kette ist durch die RC-Zeitkonstante der Abtastschalter am Eingang und durch die kapazitiv belasteten Ausgänge begrenzt. Daher ist die resultierende Bandbreite einer sechsstufigen Kette von Folge-Halte-Gliedern in 130 nm CMOS-Technologie zu gering, um Datensymbole mit einer Eingangsrate von 10 Gbaud zu verarbeiten. Daher wird das Filter mittels der Halbratenstruktur nach Abbildung 4.4 umgesetzt. Zwei miteinander verschachtelte FIR-Filter arbeiten im Gegentaktbetrieb und werden von einem differenziellen Halbraten-Takt angesteuert. Der Vorteil dieser Struktur bezüglich der Bandbreite der Signalverarbeitung in den Verzögerungsketten ist zweifach: Erstens wird die Einheitsverzögerung T nun mit einem einzigen Folge-Halte-Glied realisiert, d.h. die Länge der Verzögerungskette wird halbiert. Zum zweiten steht nun das gesamte Einheitsintervall zum Folgen zur Verfügung. Daher wird das Problem Bandbreitenbegrenzung in der Kette der kaskadierten Folge-Halte-Glieder um den Faktor vier entspannt. Das Problem der Akkumulation von nichtlinearen Verzerrungen und von Rauschen entlang der Kette von Einheitsverstärkern entspannt sich aufgrund der Halbierung der Kettenlänge um den Faktor zwei. Ein Nachteil des Halbratenkonzepts ist die notwendige Symmetrie zwischen den beiden Pfaden, aber diese kann durch ein sorgfältiges Layout der Schaltung sichergestellt werden.

Das Halbratenkonzept des Filters findet seine Fortsetzung im entscheidungsrückgekoppelten Teil des Filters. Die Addiererschaltung für die rückgekoppelten Signale wird in die Entscheider-Latches integriert. Das im Gegentakt betriebene entscheidungsrückgekoppelte Filter [14] arbeitet wie folgt: Das obere Entscheider-Latch befindet sich während der L-Phase des Taktes in seinem regenerativen Entscheidungsmodus, und das sich aufbauende entschiedene Signal wird gleichzeitig an das untere Entscheider-Latch angelegt, welches sich im Folgemodus befindet. Während der H-Phase des Taktes vertauschen sich die Rollen der beiden Entscheider-Latches.

Verglichen mit dem Entzerrer aus [9] kann der Grad der notwenigen Parallelisierung drastisch reduziert werden, der Parallelisierungsgrad ist sogar kleiner als der Grad des realisierten FIR-Filters. Daher benötigt das vorliegende Entzerrerkonzept gegenüber dem Entwurf aus [9], welches mit 8 Gbit/s eine etwas kleinere maximale Datenrate aufweist, wesentlich weniger Chipfläche und hat auch eine geringere Leistungsaufnahme: Der Entzerrer aus [9] verbraucht ca. 100 mW für den analogen FIR-Filterblock mit 4 Anzapfungen und den zugehörigen Taktgenerator mit 8 Phasen. Der hier beschriebene 10 Gbit/s-Entzerrer verbraucht 21 mW für den gesamten Filter bestehend aus dem FIR-Filter mit 3 Anzapfungen und dem DFE-Filter mit 2 Rückführungen. Zusätzlich werden 33 mW für die Takterzeugung benötigt. Insgesamt ergibt sich ein Verbrauch von nur 54 mW für eine Filterstruktur mit 5 Anzapfungen.

### 4.5 Schaltungstechnische Umsetzung

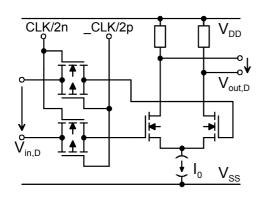

Abbildung 4.5: Folge-Halte Glied

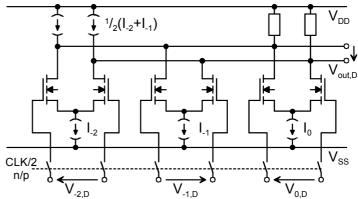

Abbildung 4.6: Getakteter Addierer für das FIR-Filter

#### Folge-Halte-Glied

Das Folge-Halte-Glied (Abbildung 4.5) besteht aus einem differenziellen komplementären Transfergatter und einem Pufferverstärker mit der Verstärkung eins. Die Haltekapazität besteht aus der Eingangskapazität des Pufferverstärkers und der halteseitigen Kapazität des Transfergatters. Die Taktpegel für die n-Kanal-Transfertransistoren werden durch eine Bootstrapschaltung angehoben, da der Gleichtaktpegel der Eingangsspannung nur etwa 300 mV unter der positiven Betriebsspannung V<sub>DD</sub> liegt. Um die Symmetrie der Taktpfade für den n-Kanal- und den p-Kanal-Transfertransistor zu gewährleisten, wird der Takt für den p-Kanal-Transfertransistor ebenfalls über eine Bootstrapschaltung geführt, welche jedoch die Taktpegel nicht anhebt. Der unipolare Taktdurchgriff wird durch die komplementäre Transfergattertopologie minimiert. Die Haltespannung wird parametrisch verstärkt, wenn das Transfergatter vom Folge- in den Haltemodus übergeht, da im Haltemodus die innere Kanalkapazität des Transfergatters verschwindet [15]. Dieser Effekt wird hingenommen, da eine lineare Verstärkung der gehaltenen Spannung die Funktionsweise des Filters nicht beeinträchtigt. Im Differenzverstärker werden relativ schmale MOSFETs verwendet und über den Lastwiderständen wird ein relativ großer Spannungsabfall eingestellt. Durch diese Dimensionierung ist der Pufferverstärker für einen maximal großen linearen Eingangs- und Ausgangsspannungsbereich ausgelegt und gleichzeitig wird die Bandbreite maximiert.

#### Getakteter Addierer für das FIR-Filter

Der getaktete Addierer für das FIR-Filter (Abbildung 4.6) besteht aus drei differenziellen Transfergattern, deren Haltespannungen jeweils einen differenziellen Transkonduktanzverstärker ansteuern. Die Ausgangsströme der Transkonduktanzverstärker werden dann über einem gemeinsamen Paar von Lastwiderständen summiert.

Bei verschiedenen Längen des Übertragungskanals und bei verschiedenen Bitraten ändert sich nur der Betrag der optimalen Koeffizienten des FIR-Filters. Daher werden die Vorzeichen der Koeffizienten durch die Polarität der differenziellen Verbindungen zwischen den Transkonduktanzverstärkern und dem Lastwiderstandspaar fest verdrahtet. Die maximalen Beträge der Koeffizienten werden durch die Dimensionierung der Weiten der MOSFETs in den jeweiligen Transkonduktanzverstärkern vorgegeben. Die Koeffizienten können durch die Ströme I.1 und I.2 angepasst werden. Die Ströme I.1 und I.2 können mittels zweier Stromspiegel und zweier externer Steuerströme eingestellt werden. Jeweils die Hälfte der Summe der Ströme I.1 und I.2 wird über weitere Stromspiegel und p-Kanal-Stromquellen in die beiden Knoten zwischen den Lastwiderständen und den Transkonduktanzverstärkern eingespeist. Dadurch wird ein konstanter Gleichtaktpegel am Ausgang des FIR-Addierers

sichergestellt. Dies ist insbesondere für den Eingang des nachfolgenden DFE-Addierers wichtig und verhindert eine Degeneration der Steilheit der Transkonduktanzverstärker, wenn große Koeffizientenwerte eingestellt werden.

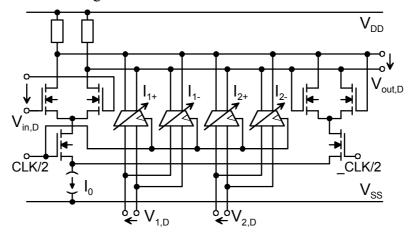

Abbildung 4.7: DFE-Entscheider-Latch mit integriertem Addierer

#### DFE-Entscheider-Latch mit integriertem Addierer

Der Addierer für das entscheidungsrückgekoppelte Filter ist in das Entscheider-Latch in Stromschalterlogik (engl. *current mode logic*, *CML*) integriert (Abbildung 4.7). Die Eingangsspannung liegt an einem getakteten Transkonduktanzverstärker an. Während der Folgephase werden die rückgekoppelten Signale über einstellbare Transkonduktanzverstärker zum Eingangssignal addiert. Für positives und negatives Vorzeichen ist jeweils ein eigener Transkonduktanzverstärker vorgesehen. Das Vorzeichen wird ausgewählt, indem der Steuerstrom für den jeweiligen Koeffizienten in den entsprechenden Stromspiegeleingang für positives oder negatives Vorzeichen eingespeist wird. Die Entscheidung wird von dem mit dem komplementären Taktsignal angesteuerten kreuzgekoppelten Transkonduktanzverstärker getroffen.

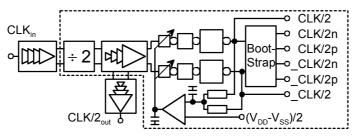

Abbildung 4.8: Taktgenerator

#### **Taktgenerator**

Für den Entzerrerkern werden sechs unipolare Taktsignale benötigt. Der entscheidungsrückgekoppelte Entzerrer arbeitet mit einem komplementären Paar von CMOS-Taktsignalen mit vollem Hub (von V<sub>SS</sub> bis V<sub>DD</sub>). Die Folge-Halte-Glieder und die getakteten FIR-Addierer benötigen zwei komplementäre Paare von Taktsignalen mit großem Hub und teilweise angehobenen Logikpegeln, wobei jeweils ein Paar für den n-Kanal- und den p-Kanal-Transfertransistor vorgesehen ist. Abbildung 4.8 zeigt die Struktur des Taktgenerators. Das von außen zugeführte unipolare Vollraten-Taktsignal wird zunächst über eine Differenzverstärkerkette verstärkt und symmetrisiert, bevor es mit zwei rückgekoppelten CML-Latches durch zwei geteilt wird. Das differenzielle Halbraten-Taktsignal wird dann zunächst über eine Kette von vier CML-Differenzverstärkern und dann über zwei parallele

Ketten von jeweils drei CMOS-Invertern geführt. Das Taktsignal wird in den beiden Ketten auf den vollen CMOS-Spannungshub verstärkt und auf ein niedriges Impedanzniveau gebracht, damit die kapazitive Last des Entzerrerkerns umgeladen werden kann. Damit die Daten am Eingang des Entzerrers präzise zu äquidistanten Zeitpunkten abgetastet werden, muss für das Halbraten-Taktsignal ein Tastverhältnis von 1:1 am Ausgang der Verstärkerketten sichergestellt werden. Daher wird die Entscheiderschwelle des ersten CMOS-Inverters in der CMOS-Inverterkette über einen Regelkreis nachgeregelt. Der Regelverstärker misst das Tastverhältnis am Ausgang der CMOS-Inverterkette und regelt die Entscheiderschwelle entsprechend nach. Die Taktsignale für die Transfertransistoren werden über Bootstrapschaltungen geführt, welche MOSFETs und Kondensatoren enthalten.

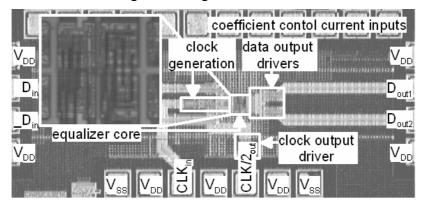

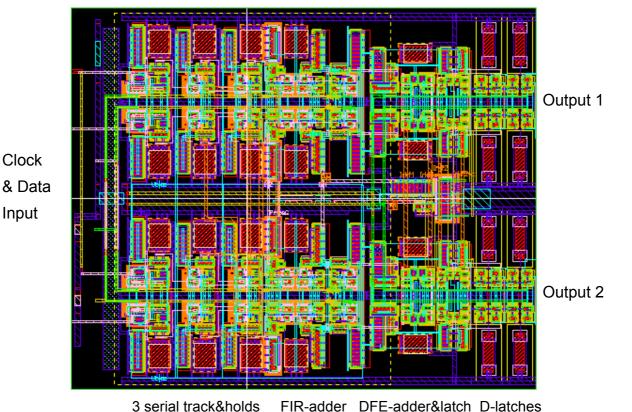

Abbildung 4.9 zeigt eine Fotografie des gesamten Entzerrerchips und in Abbildung 4.10 ist das Layout des Entzerrerkerns vergrößert dargestellt.

**Abbildung 4.9:** Fotografie des Entzerrers mit einer Vergrößerung des Entzerrerkerns. Gesamte Chipfläche: ca. 1400 μm x 600 μm. Fläche des Entzerrerkerns: 60 μm x 56 μm.

**Abbildung 4.10:** Layout des voll-symmetrischen Kerns des Halbraten-Entzerrers (ca. 60 μm x 56 μm)

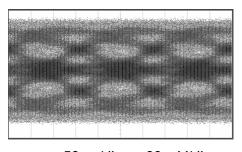

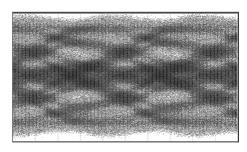

# 4.6 Messergebnisse

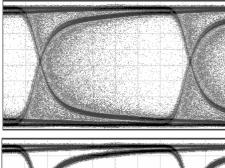

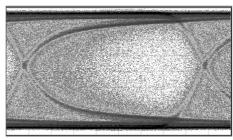

x: 50 ps/div, y: 60 mV/div

x: 25 ps/div, y: 60 mV/div

x: 50 ps/div, y: 50 mV/div

x: 25 ps/div, y: 60 mV/div

173 cm lange Leitung auf FR4 bei 6 Gbit/s

90 cm lange Leitung auf FR4 bei 10 Gbit/s

**Abbildung 4.11:** PRBS-Datenübertragung der Länge  $2^{31}$ -1 (Spannungshub  $V_{pp,PPG} = 400 \text{mV}$ ): Oben: Augendiagramm des Vollraten-Datensignals am Ende der 173 cm bzw. 90 cm langen Leitung. Mitte: Augendiagramm des Halbraten-Datenausgangs des Entzerrers bei ausgeschalteter Entzerrung. Unten: Augendiagramm des Halbraten-Datenausgangs des Entzerrers bei eingeschalteter Entzerrung.

173 cm lange Leitung auf FR4 bei 6 Gbit/s

90 cm lange Leitung auf FR4 bei 10 Gbit/s

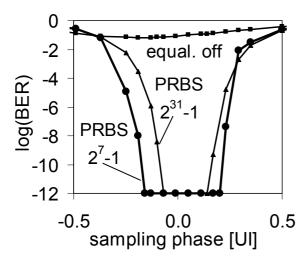

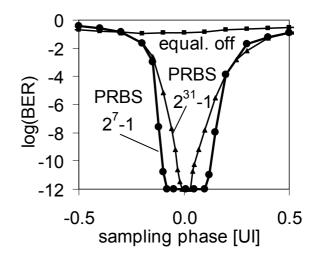

**Abbildung 4.12:** Gemessene Bitfehlerrate aufgetragen gegenüber der Abtastphase (Spannungshub  $V_{pp,PPG} = 400 \text{mV}$ , Entzerrerkoeffizienten jeweils konstant).

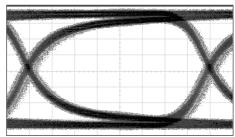

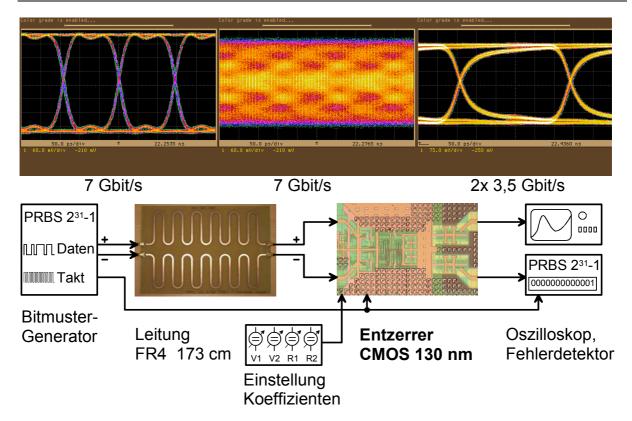

Abbildung 4.13: Entzerrung eines binären 7 Gbit/s PRBS-Datensignals der Länge 2<sup>31</sup>-1, welches über eine differenzielle 173 cm lange Mikrostreifenleitung auf FR4-Platinenmaterial geführt wird.

Links: Augendiagramm des 7 Gbit/s Ausgangssignals des Bitmustergenerators.

Mitte: Augendiagramm des verzerrten 7 Gbit/s Signals nach der 173 cm langen Leitung.

Rechts: Augendiagramm eines der beiden 3,5 Gbit/s Ausgangssignale des Entzerrers.

Unten: Messaufbau mit Bitmustergenerator, Leitung, Entzerrer, Abtastoszilloskop und Fehlerdetektor.

| Betriebsspannung V <sub>DD</sub>                                                                        | 1,3 V      | P <sub>DC</sub> Entzerrer*               | 21 mW  |

|---------------------------------------------------------------------------------------------------------|------------|------------------------------------------|--------|

| Maximale Bitrate f <sub>max</sub>                                                                       | 10 Gbit/s  | P <sub>DC</sub> Taktgenerator**          | 33 mW  |

| Minimale Bitrate f <sub>min</sub>                                                                       | 0,5 Gbit/s | P <sub>DC</sub> insgesamt (mit Treibern) | 200 mW |

| Maximale Kanaldämpfung bei Nyquistfreq. für BER < 10 <sup>-12</sup> , PRBS 2 <sup>31</sup> -1, 7 Gbit/s |            |                                          | 24 dB  |

| Minimaler Hub $V_{pp,PPG}$ für BER $< 10^{-11}$ , PRBS $2^7$ -1, 10 Gbit/s, 90 cm FR4                   |            |                                          | 300 mV |

| Minimaler Hub $V_{pp,PPG}$ für BER $< 10^{-11}$ , PRBS $2^7$ -1, 6 Gbit/s, 173 cm FR4                   |            |                                          | 230 mV |

\*Schaltungsblöcke entsprechend Abbildung 4.4,

Tabelle 4.1: Zusammenstellung der Eigenschaften des Entzerrers.

Der differentielle Übertragungskanal wird von den differentiellen Ausgängen eines Anritsu MP1763C Bitmustergenerators (engl. *pulse pattern generator, PPG*) gespeist. Die Ausgänge der Leitungen und das Vollraten-Taktsignal des PPG werden mittels on-Wafer-Messspitzen mit den entsprechenden Eingängen des Entzerrers verbunden. Die Halbraten- Daten- und Taktausgänge des Entzerrers werden an einen Bitfehlerdetektor (engl. *error detector, ED*) und an ein Abtastoszilloskop mit 20 GHz Bandbreite angeschlossen (vergleiche Abbildung 4.13). Pseudozufällige Datenfolgen (*pseudo random bit sequence, PRBS*) mit den Längen 2<sup>7</sup>-1 und 2<sup>31</sup>-1 werden zur Bestimmung der Bitfehlerrate (engl. *bit error rate, BER*) verwendet. Die Entzerrerkoeffizienten werden von Hand über externe Stromquellen eingestellt.

<sup>\*\*</sup>Schaltungsblöcke in der gestrichelten Umrandung in Abbildung 4.8.

Die am Ausgang der Leitung gemessenen Augendiagramme sind in Abbildung 4.11 oben dargestellt. Sie sind komplett geschlossen. Die Augendiagramme an einem der beiden Halbraten-Ausgänge bei ausgeschalteter Entzerrung (alle einstellbaren Entzerrerkoeffizienten sind gleich null gesetzt) sind darunter dargestellt. Da der Entzerrer getaktet arbeitet und da die Latches im DFE-Entzerrer und die Ausgangstreiberketten eine nicht unerhebliche Verstärkung aufweisen, entsteht auch bei Ausgeschalteter Entzerrung der Eindruck eines Auges. Viele Entscheidungen sind jedoch falsch oder bleiben metastabil. Die metastabilen Entscheidungen sind an den Punkten im Inneren des Auges zu erkennen. Wenn die Entzerrung mit den optimal eingestellten Koeffizienten aktiviert wird, öffnet sich das Auge und die metastabilen Entscheidungen verschwinden. Die Bitfehlerrate ist in Abbildung 4.12 gegenüber der Abtastphase aufgetragen. Die Abtastphase wird über die einstellbare Verzögerungszeit des Taktes am PPG eingestellt. Wenn die Entzerrung eingeschaltet ist, ergibt sich am Eingang des Entzerrers ein virtuelles Auge. In Tabelle 4.1 sind die Eigenschaften des Entzerrers zusammengestellt. Der Entzerrer kann bei 7 Gbit/s eine Kanaldämpfung von bis zu 24 dB (gemessen bei der Nyquistfrequenz von 3,5 GHz) ausgleichen. Der mindestens erforderliche unipolare Spannungshub V<sub>pp,PPG</sub> am Eingang des Leitungspaares beträgt bei Kanälen mit 18 bis 19 dB Dämpfung 300 mV bei 10 Gbit/s und 230 mV bei 6 Gbit/s.

### 4.7 Fazit

Es wurde ein Abtastentzerrer für Datenraten zwischen 0,5 Gbit/s und 10 Gbit/s vorgestellt. Die durch das kombinierte FIR-DFE-Filter entstehende Entzerrungscharakteristik kann durch die getaktete Arbeitsweise des Entzerrers in der Frequenz kontinuierliche verschoben bzw. gestreckt werden. Es können Kanaldämpfungen bis 24 dB kompensiert werden, wobei die Leistungsaufnahme des Entzerrerkerns nur 21 mW und des Taktgenerators nur 33 mW beträgt. Die Fläche des Entzerrerkerns beträgt nur 60 μm x 56 μm. Eine automatische Einstellung und Adaption der Entzerrerkoeffizienten muss in weiteren Arbeiten angegangen werden.

### Literaturverzeichnis

- [1] M. Horowitz, C.-K. K. Yang, S. Sidriopoulos, "High-speed electrical signaling: overview and limitations", *IEEE Micro*, vol. 18, no. 1, pp. 12-24, January/February 1998.

- [2] J. Liu, X. Lin, "Equalization in high-speed communication systems", *IEEE Circuits and Systems Magazine*, vol. 4, no. 2, pp. 4-17, April 2004.

- [3] W. J. Dally, J. Poulton "Transmitter Equalization for 4-Gbps signaling", *IEEE Micro*, vol. 17, no. 1, pp. 48-56, January/February 1998.

- [4] R. Payne et al, "A 6.25-Gb/s binary transceiver in 0.13-μm CMOS for serial data transmission across high loss legacy backplane channels", *IEEE JSSC*, vol. 40, no. 12, pp. 2646-2657, December 2005.

- [5] T. Beukema et al., "A 6.4-Gb/s CMOS SerDes core with feed-forward and decision-feedback equalization", *IEEE JSSC*, vol. 40, no. 12, pp. 2646-2657, December 2005.

- [6] S. Reynolds, P. Pepeljugoski, J. Schaub, J. Tierno, D. Beisser, "A 7-tap transverse analog-FIR filter in 0.13μm CMOS for equalization of 10Gb/s fiber-optic data systems", *ISSCC* 2005, pp. 330-331, February 2005.

- [7] G. T. Uehara, "Parallelism in analog and digital PRML magnetic disk read channel equalizers", *IEEE Transactions on Magnetics*, vol. 31, no. 2, pp 1174- 1179, March 1995.

- [8] D. Xu, Y. Song, T. Uehara, "A 200 MHz 9-tap analog equalizer for magnetic disk read channels in 0.6μm CMOS", *ISSCC 1996*, pp. 74-75, February 1996.

- [9] J. E. Jaussi et al., "8-Gb/s source-synchronous I/O link with adaptive receiver equalization, offset cancellation, and clock de-skew," *IEEE JSSC*, vol. 40 no. 1, pp. 80-88, January 2005.

- [10] R. Gomez, M. Rofougaran, A. A. Abidi, "A Discrete-Time Analog Signal Processor for Disk Read Channels", *ISSCC 1993*, pp 212-213, February 1993.

- [11] P. Capofreddi, "Analog FIR filter with parallel interleaved architecture", *United States Patent* US 6,553,398 B2, April 2003.

- [12] G. Kanter, P. Capafreddi, S. Behtash, A. Gandhi, "Electronic equalization for extending the reach of electro-absorption modulator based transponders", *OFC 2003*, pp. 476-477, March 2003.

- [13] G. S. Kanter, A. K. Samal, O. Coskun and A. Gandhi, "Electronic equalization for enabling communications at OC-192 rates using OC-48 components", *Optics Express*, vol. 11, no. 17, August 2003.

- [14] Y.-S. Sohn, S.-J. Bae, H.-J. Park, S.-I. Cho, "A 1.2 Gbps CMOS DFE receiver with the extended sampling time window for application to the SSTL channel," *2002 Symp. on VLSI Circuits*, pp. 92-93, February 2005.

- [15] S. Ranganathan, Y. Tsividis, "Discrete-time parametric amplification based on a three-terminal MOS varactor: analysis and experimental results," *IEEE JSSC*, vol. 38 no. 12, pp. 2087-2093, December 2003.